Altera ALTDQ_DQS2 User Manual

Page 52

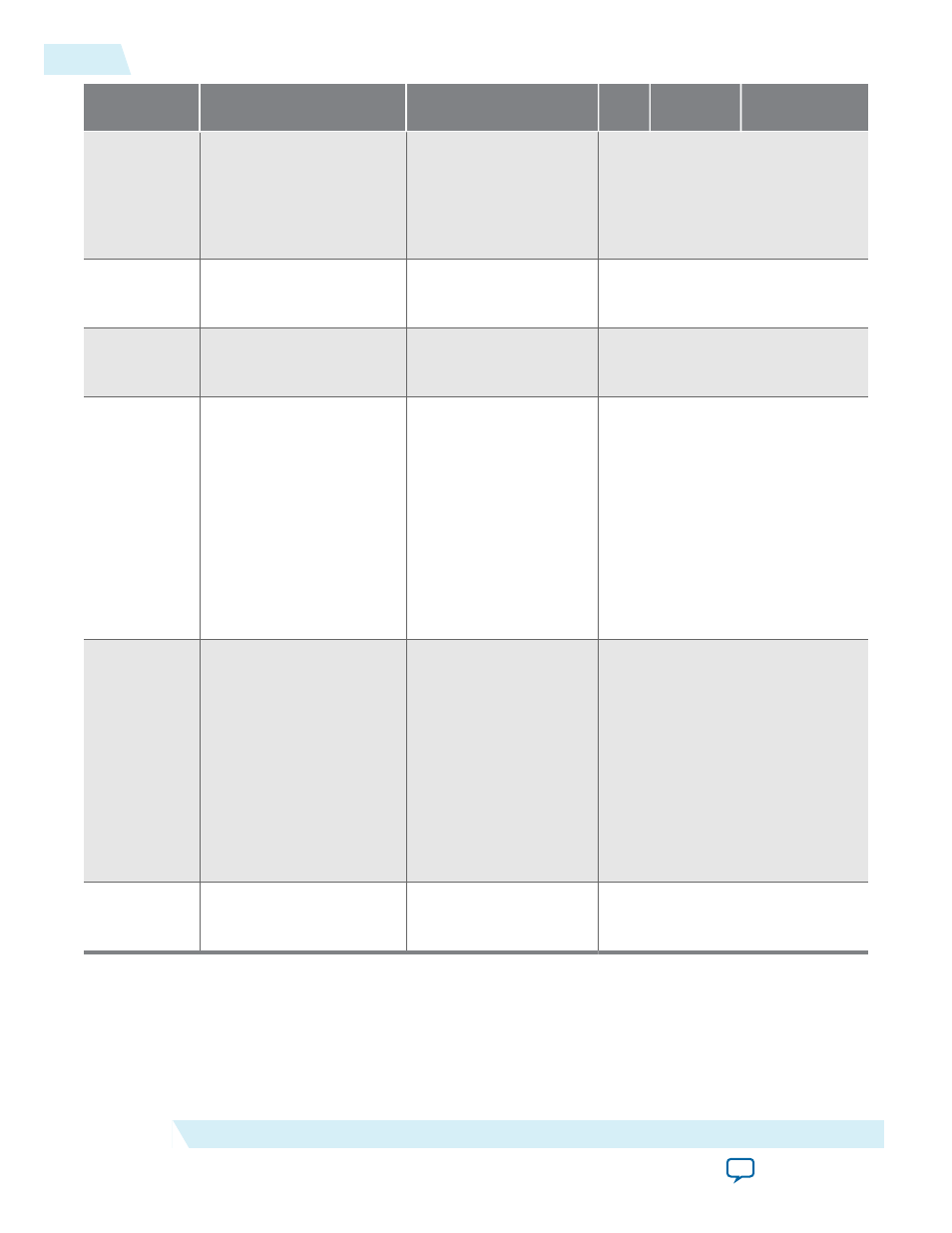

Bit

Bit Name

Default Value (Binary)

Min

Value

Max Value

Inc. Unit

88..87

dqsinputphasesetting

0

00 = 0°

01 = 45°

10 = 90°

11 = 135°

89

enadqsphasetransferreg

0

0 = bypass

1 = enable

90

enaoutputphasetransferreg

0

0 = bypass

1 = enable

93..91

enadqscycledelaysetting

10

000: Not supported

001: Not supported

010: No delay

011: 1 cycle delay

100: 2 cycle delay

101: 3 cycle delay

110: Not supported

111: Not supported

96..94

enaoutputcycledelaysetting

10

000: Not supported

001: Not supported

010: No delay

011: 1 cycle delay

100: 2 cycle delay

101: 3 cycle delay

110: Not supported

111: Not supported

100..97

enainputcycledelaysetting

enainputphasetransferreg

0

—

Related Information

•

52

DQS Configuration Block Bit Sequence for Arria V GZ and Stratix V Devices

UG-01089

2014.12.17

Altera Corporation

ALTDQ_DQS2 IP Core User Guide