Altera Reed-Solomon II MegaCore Function User Manual

Page 24

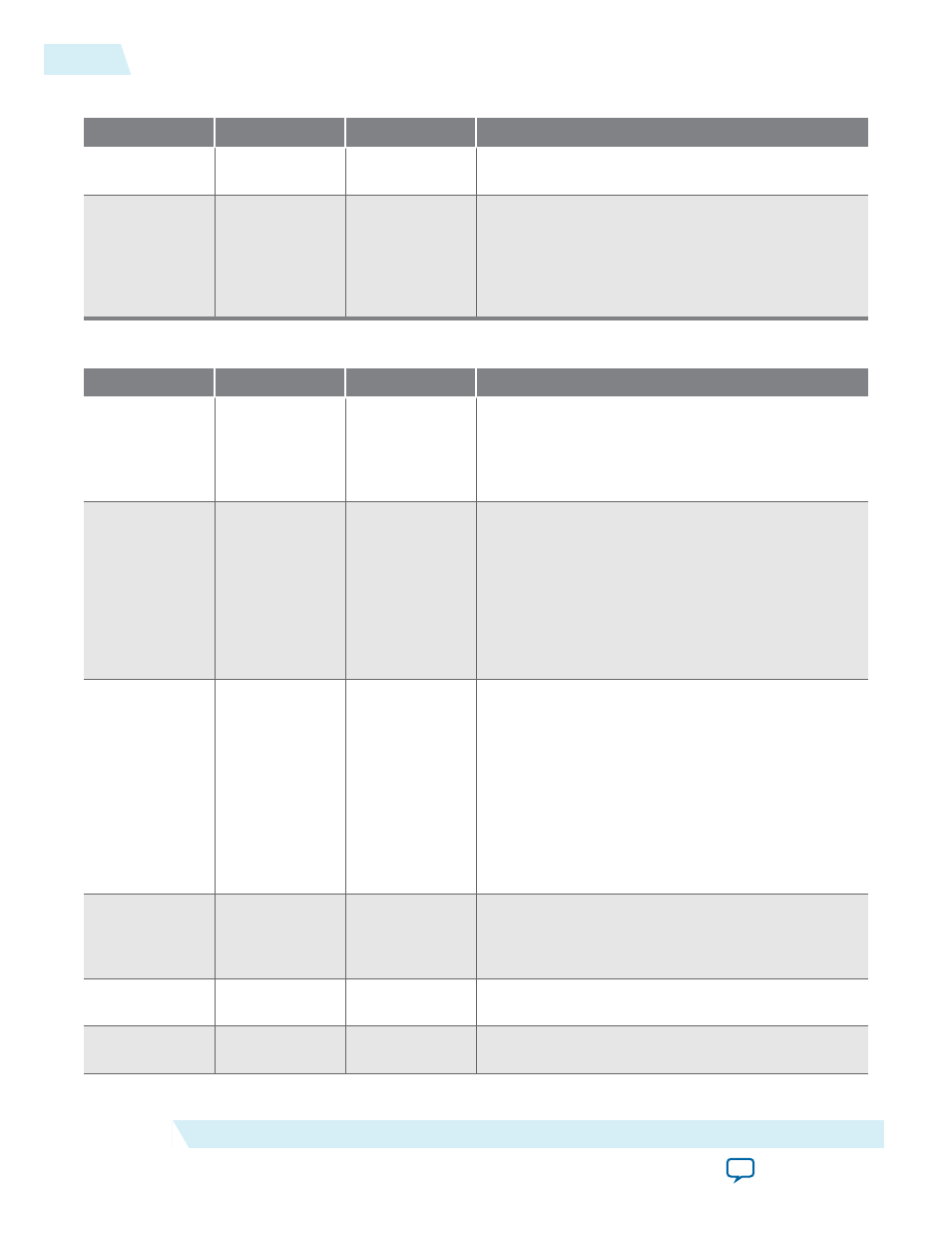

Table 3-3: Clock and Reset Signals

Name

Avalon-ST Type

Direction

Description

clk_clk

clk

Input

The main system clock. The whole IP core operates

on the rising edge of

clk_clk

.

reset_

reset_n

reset_n

Input

An active low signal that resets the entire system

when asserted. You can assert this signal asynchro‐

nously. However, you must deassert it synchronous

to the

clk_clk

signal. When the IP core recovers

from reset, ensure that the data it receives is a

complete packet.

Table 3-4: Avalon-ST Input and Output Interface Signals

Name

Avalon-ST Type

Direction

Description

in_ready

ready

Output

Data transfer ready signal to indicate that the sink is

ready to accept data. The sink interface drives the

in_ready

signal to control the flow of data across

the interface. The sink interface captures the data

interface signals on the current

clk

rising edge.

in_valid

valid

Input

Data valid signal to indicate the validity of the data

signals. When you assert the

in_valid

signal, the

Avalon-ST data interface signals are valid. When

you deassert the

in_valid

signal, the Avalon-ST

data interface signals are invalid and must be

disregarded. You can assert the

in_valid

signal

whenever data is available. However, the sink only

captures the data from the source when the IP core

asserts the

in_ready

signal.

in_data[]

data

Input

Data input for each codeword, symbol by symbol.

Valid only when you assert the

in_valid

signal. For

Qsys systems, the

in_data

bus is:

[

numn

,

numcheck

,

data

] If you have no variable check

it is: [

numn

,

data

]

For example, for a maximum codeword length of

255 corresponding to 8 bits:

•

in_data[7:0]

=

data

•

indata_[15:0]

=

numn

in_channel

channel

Input

Specifies the channel number for data the IP core

transfers on the current cycle. The

in_channe

l

signal is available only when you configure the IP

core to support multiple channels.

in_startof-

packet

sop

Input

Start of packet (codeword) signal.

in_

endofpacket

eop

Input

End of packet (codeword) signal.

3-8

Reed-Solomon II IP Core Signals

UG-01090

2015.05.01

Altera Corporation

Reed-Solomon II IP Core Functional Description