Measurement Computing ACC-300 User Manual

Page 5

Page 5

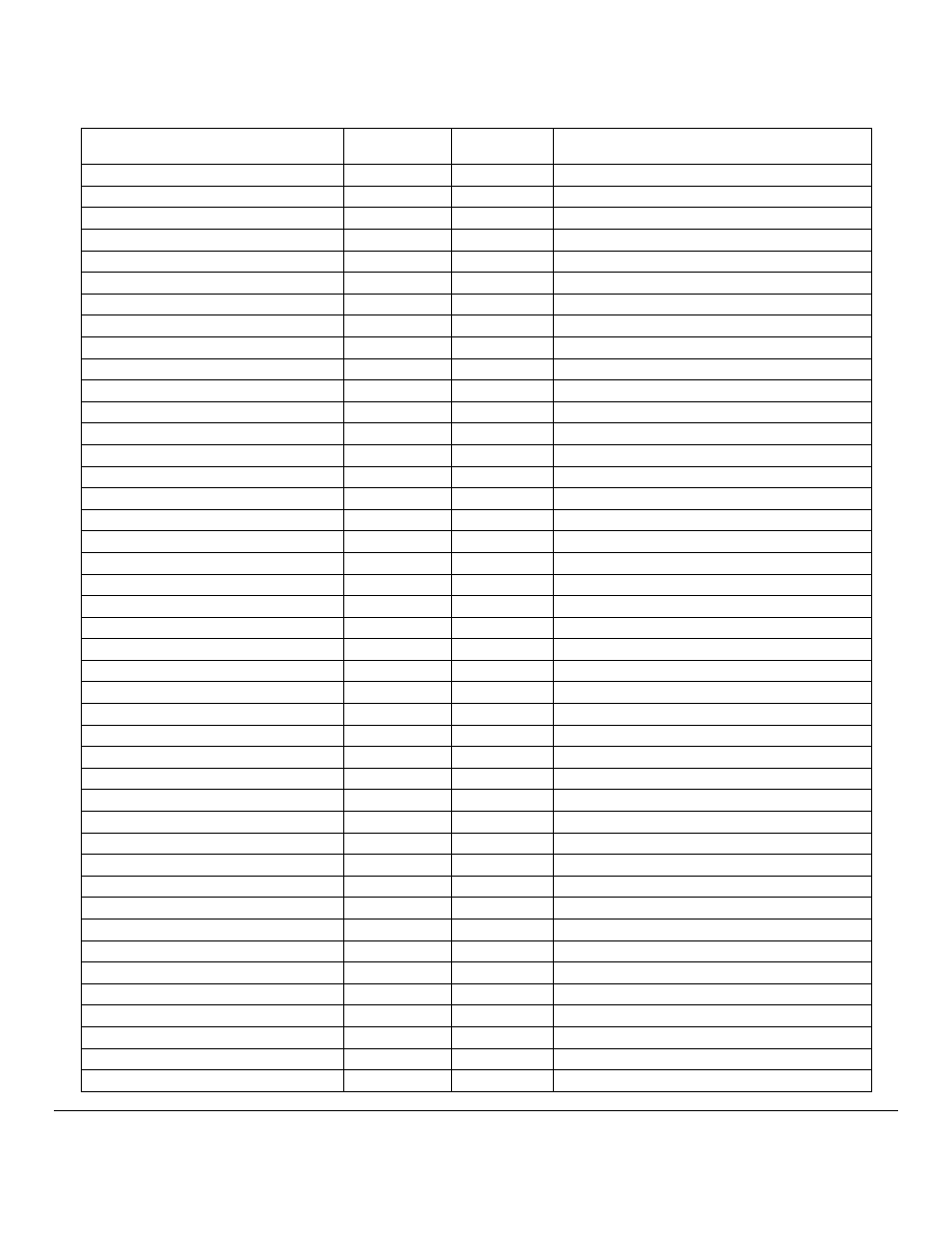

Signal mapping between the PCI-DAS1xxx and PCI-DAS6000

The table below lists how the signals are mapped between the board connector on PCI-DAS1xxx Series hardware and the board

connector on PCI-DAS6000 Series hardware.

PCI-DAS6000 signal name

PCI-DAS6000

pin number

PCI-DAS1Xxx

pin number

Signal name

LLGND

1

1

LLGND

CH0 IN

2

2

CH0 IN

CH8 IN

3

3

CH8 IN

CH1 IN

4

4

CH1 IN

CH9 IN

5

5

CH9 IN

CH2 IN

6

6

CH2 IN

CH10 IN

7

7

CH10 IN

CH3 IN

8

8

CH3 IN

CH11 IN

9

9

CH11 IN

CH4 IN

10

10

CH4 IN

CH12 IN

11

11

CH12 IN

CH5 IN

12

12

CH5 IN

CH13 IN

13

13

CH13 IN

CH6 IN

14

14

CH6 IN

CH14 IN

15

15

CH14 IN

CH7 IN

16

16

CH7 IN

CH15 IN

17

17

CH15 IN

LLGND

18

18

LLGND

AISENSE

35

19

NEW - AISENSE INPUT formerly N/C

D/A GND

37

35

D/A GND0

D/A OUT0

36

36

D/A OUT0

D/A GND

37

37

D/A GND1

D/A OUT1

38

38

D/A OUT1

PC +5V

39

48

PC +5V

AUXOUT0 / CTR2_CLK

40

77

10 MHz OUT

AUXOUT0 / D/A PACER OUT (default)

40

96

D/A INTERNAL PACER OUTPUT

AUXOUT1 / A/D PACER OUT (default)

41

95

A/D INTERNAL PACER OUTPUT

AUXOUT2 / SSH_OUT

42

49

SSH OUT

AUXIN0 / A/D CONVERT (default)

43

42

A/D EXTERNAL PACER

AUXIN0 / ATRIG

43

43

ANALOG TRIGGER IN

AUXIN1 / A/D START TRIGGER (default)

45

45

A/D EXTERNAL TRIGGER

AUXIN2 / A/D STOP TRIGGER (default)

46

46

NEW - AUXIN2 INPUT formerly N/C

AUXIN3 / D/A UPDATE (default)

47

44

D/A EXTERNAL PACER IN

AUXIN4 / D/A START TRIGGER (default)

48

97

EXTERNAL D/A PACER GATE

AUXIN5 / A/D PACER GATE (default)

49

47

NEW - AUXIN5 INPUT formerly N/C

GND

50

50

GND

FIRSTPORTA Bit 0

51

51

FIRSTPORTA Bit 0

FIRSTPORTA Bit 1

52

52

FIRSTPORTA Bit 1

FIRSTPORTA Bit 2

53

53

FIRSTPORTA Bit 2

FIRSTPORTA Bit 3

54

54

FIRSTPORTA Bit 3

FIRSTPORTA Bit 4

55

55

FIRSTPORTA Bit 4

FIRSTPORTA Bit 5

56

56

FIRSTPORTA Bit 5

FIRSTPORTA Bit 6

57

57

FIRSTPORTA Bit 6