6 dma, interrupt & trigger control – Measurement Computing PC104-DAS16JR/12 User Manual

Page 20

3.6 DMA, INTERRUPT & TRIGGER CONTROL

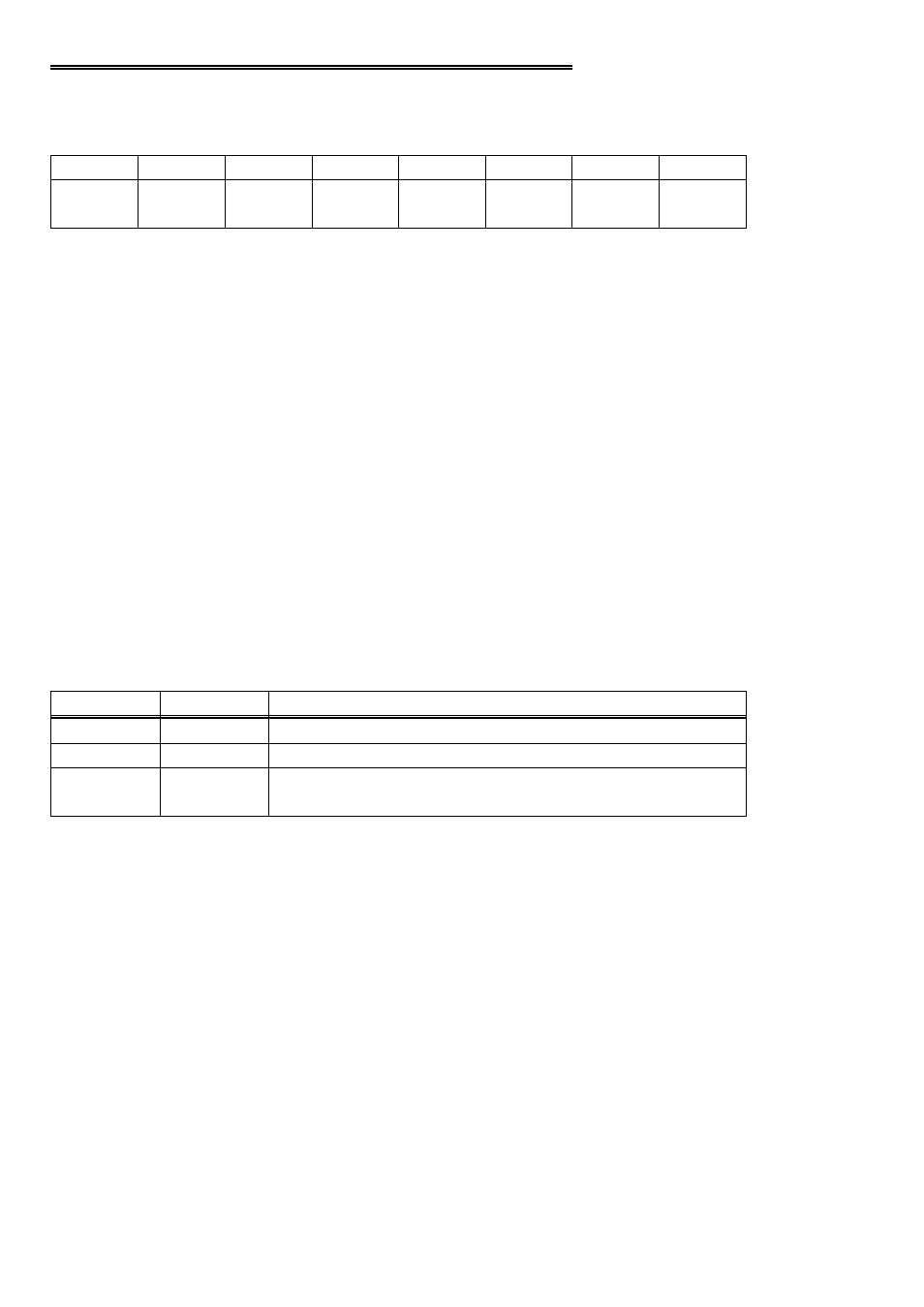

BASE ADDRESS + 9

TS0

TS1

DMA

Don’t

Care

IR1

IR2

IR4

INTE

0

1

2

3

4

5

6

7

A read and write register.

READ

INTE = 1, Interrupts are enabled. An interrupt generated will be placed on the

PC bus interrupt level selected by IR4, IR2 & IR1. INTE = 0, interrupts are

disabled.

IR4, IR2, IR1 are bits in a binary number between 0 and 7 which map interrupts

onto the PC bus interrupt levels 2 - 7. Interrupts 0 & 1 may not be asserted by the

PC104-DAS16Jr/xx.

DMA = 1, DMA transfers are enabled. DMA = 0, DMA transfers are disabled.

It is worth noting that this bit only allows the PC104-DAS16Jr/xx to assert a

DMA request to the PC on the DMA request level selected by the DMA switch

on the PC104-DAS16Jr/xx. Before this bit is set to 1, the PC's 8237 (or

appropriate) DMA controller chip must be set up.

TS1 & TS0 control the source of the A/D start conversion trigger according to

Table 4-4 below.

Table 3-3. A/D Start Conversion Source Coding

Start on Pacer Clock Pulse (CTR 2 OUT, no external

access)

1

1

Start on rising TRIGGER (Digital input 0, Pin 25)

0

1

Software triggered A/D only.

X

0

TS0

TS1

16