Chapter 3, Motherboard information – Lanner VES-220 User Manual

Page 16

13

Motherboard Information

Chapter 3

Embedded and Industrial Computing

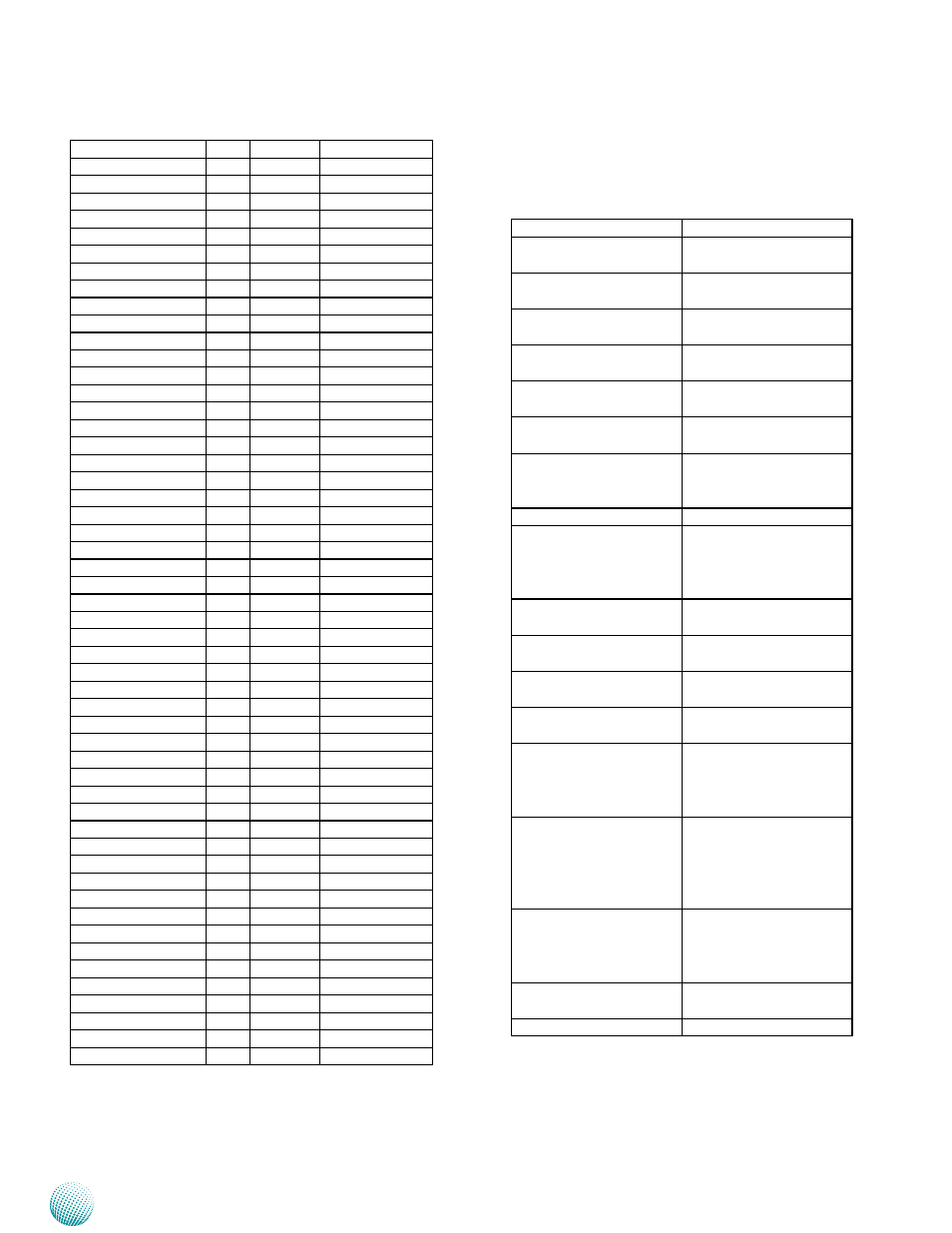

Signal

PIN

PIN

Signal

NC

C59

D59

NC

GND

C60

D60

GND

NC

C61

D61

NC

NC

C62

D62

NC

NC

C63

D63

NC

NC

C64

D64

NC-

NC

C65

D65

NC

NC

C66

D66

NC

NC

C67

D67

GND

NC

C68

D68

NC

NC

C69

D69

NC

GND

C70

D70

GND

NC

C71

D71

NC

NC

C72

D72

NC

NC

C73

D73

NC

NC

C74

D74

NC

NC

C75

D75

NC

GND

C76

D76

GND

NC

C77

D77

IDE_CBLID#

NC

C78

D78

NC

NC

C79

D79

NC

GND

C80

D80

GND

NC

C81

D81

NC

NC

C82

D82

NC

NC

C83

D83

NC

GND

C84

D84

GND

NC

C85

D85

NC

NC

C86

D86

NC

GND

C87

D87

GND

NC

C88

D88

NC

NC

C89

D89

NC

GND

C90

D90

GND

NC

C91

D91

NC

NC

C92

D92

NC

GND

C93

D93

GND

NC

C94

D94

NC

NC

C95

D95

NC

GND

C96

D96

GND

NC

C97

D97

NC

NC

C98

D98

NC

NC

C99

D99

NC

GND

C100 D100

GND

NC

C101 D101

NC

NC

C102 D102

NC

GND

C103 D103

GND

VCC_12V

C104 D104

VCC_12V

VCC_12V

C105 D105

VCC_12V

VCC_12V

C106 D106

VCC_12V

VCC_12V

C107 D107

VCC_12V

VCC_12V

C108 D108

VCC_12V

VCC_12V

C109 D109

VCC_12V

GND

C110 D110

GND

Signal Descriptions of CN1B:

PCI Signals

•

Signal

Signal Description

PCI_AD[0:31]

PCI bus multiplexed ad-

dress and data lines.

PCI_C/BE[0:3]#

PCI bus byte enable lines,

active low.

PCI_DEVSEL#

PCI bus Device Select,

active low.

PCI_FRAME#

PCI bus Frame control

line, active low.

PCI_IRDY#

PCI bus Initiator Ready

control line, active low.

PCI_TRDY#

PCI bus Target Ready

control line, active low.

PCI_STOP#

PCI bus STOP control

line, active low, driven by

cycle initiator.

PCI_PAR

PCI bus parity.

PCI_PERR#

Parity Error: An external

PCI device drives PERR#

when it receives data that

has a parity error.

PCI_REQ[0:3]#

PCI bus master request

input lines, active low.

PCI_ GNT[0:3]#

PCI bus master grant out-

put lines, active low.

PCI_RESET#

PCI Reset output, active

low.

PCI_LOCK#

PCI Lock control line, ac-

tive low.

PCI_SERR#

System Error: SERR# may

be pulsed active by any

PCI device that detects a

system error condition.

PCI_PME#

PCI Power Management

Event: PCI peripher-

als drive PME# to wake

system from low-power

states S1-S5.

PCI_CLKRUN#

Bidirectional pin used

to support PCI clock

run protocol for mobile

systems.

PCI_IRQ[A:D]#

PCI interrupt request

lines.

PCI_CLK

PCI 33MHz clock output.