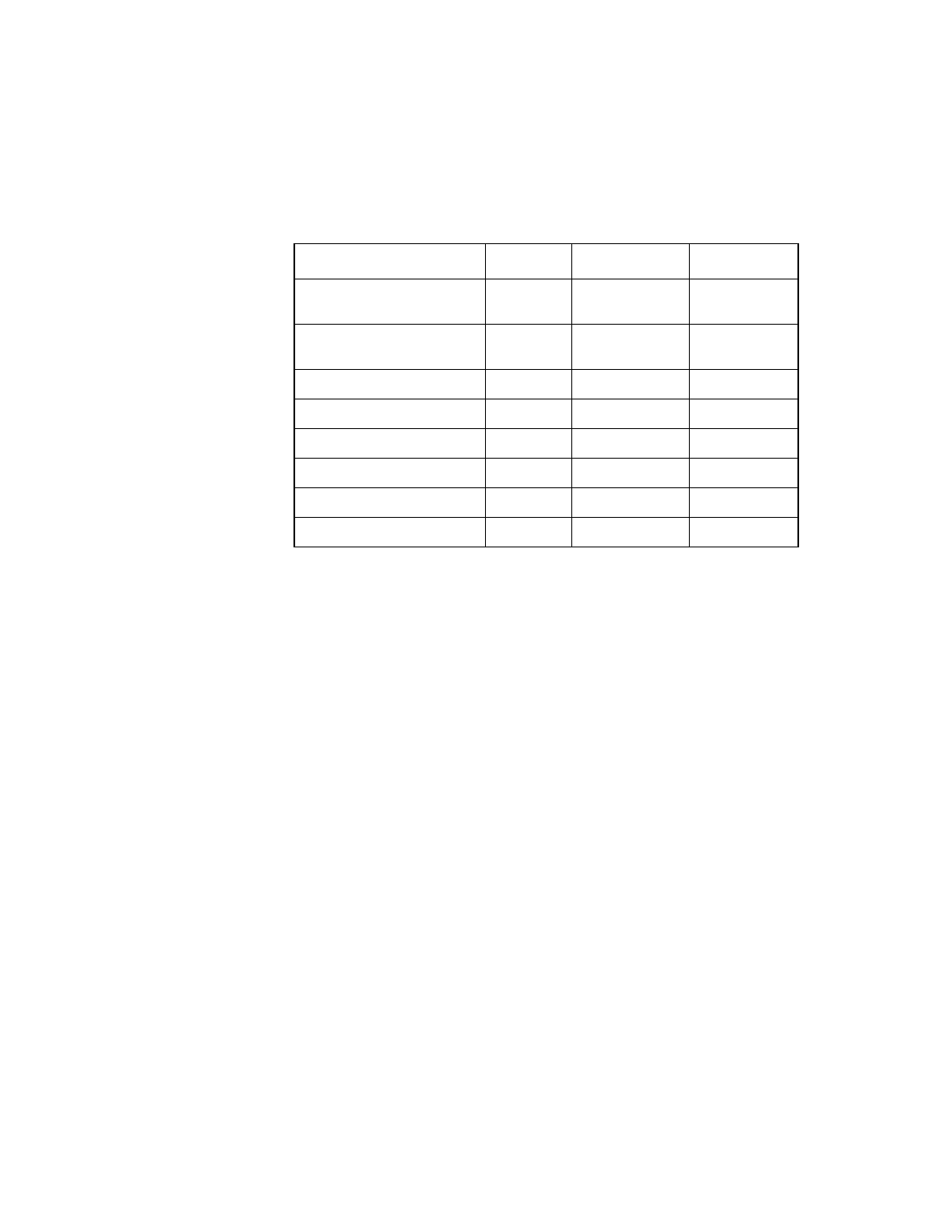

Table 3.4 scsi phase bit values (call format), Scsi phase bit values (call format) – Avago Technologies LSI53C1010 User Manual

Page 47

Instruction Descriptions

3-7

Register

Definition(s)

The information listed below describes the DBC and DSPS registers:

Table 3.4

SCSI Phase Bit Values (CALL Format)

1

1. 0 - False, negated; 1 - True, asserted. For these phases, SEL is negated and

BSY is asserted.

Phase

Message

Command/Data

Input/Output

DATA_OUT

2

(ST_DATA_OUT)

3

2. All chips except LSI53C10XX.

3. LSI53C10XX chips.

0

0

0

DATA_IN

2

(ST_DATA_IN)

3

0

0

1

COMMAND

0

1

0

STATUS

0

1

1

RES4

4

(DT_DATA_OUT)

3

4. RES4 and RES5 are reserved SCSI phases except in the LSI53C10XX chips.

1

0

0

RES5

4

(DT_DATA_IN

)3

1

0

1

MESSAGE_OUT

1

1

0

MESSAGE_IN

1

1

1

Relative Address

Mode

Relative Addressing Mode indicates that the 24-bit value in

DSPS is to be used as an offset from DSP.

Carry Test

When this bit is set, True/False comparisons may be made

based on the ALU Carry bit.

True

Transfer on TRUE/FALSE condition.

0 - Transfer if condition is FALSE

1 - Transfer if condition is TRUE

Compare Data

Compare data byte to first byte of the received data.

0 - Do not compare data

1 - Perform comparison

Compare Phase

Compare current SCSI phase to SCSI phase field or SATN/.

This bit is set whenever the Phase operand is used.

0 - Do not compare phase

1 - Perform comparison