Measurement Computing CIO-DAS-TEMP User Manual

Page 16

Advertising

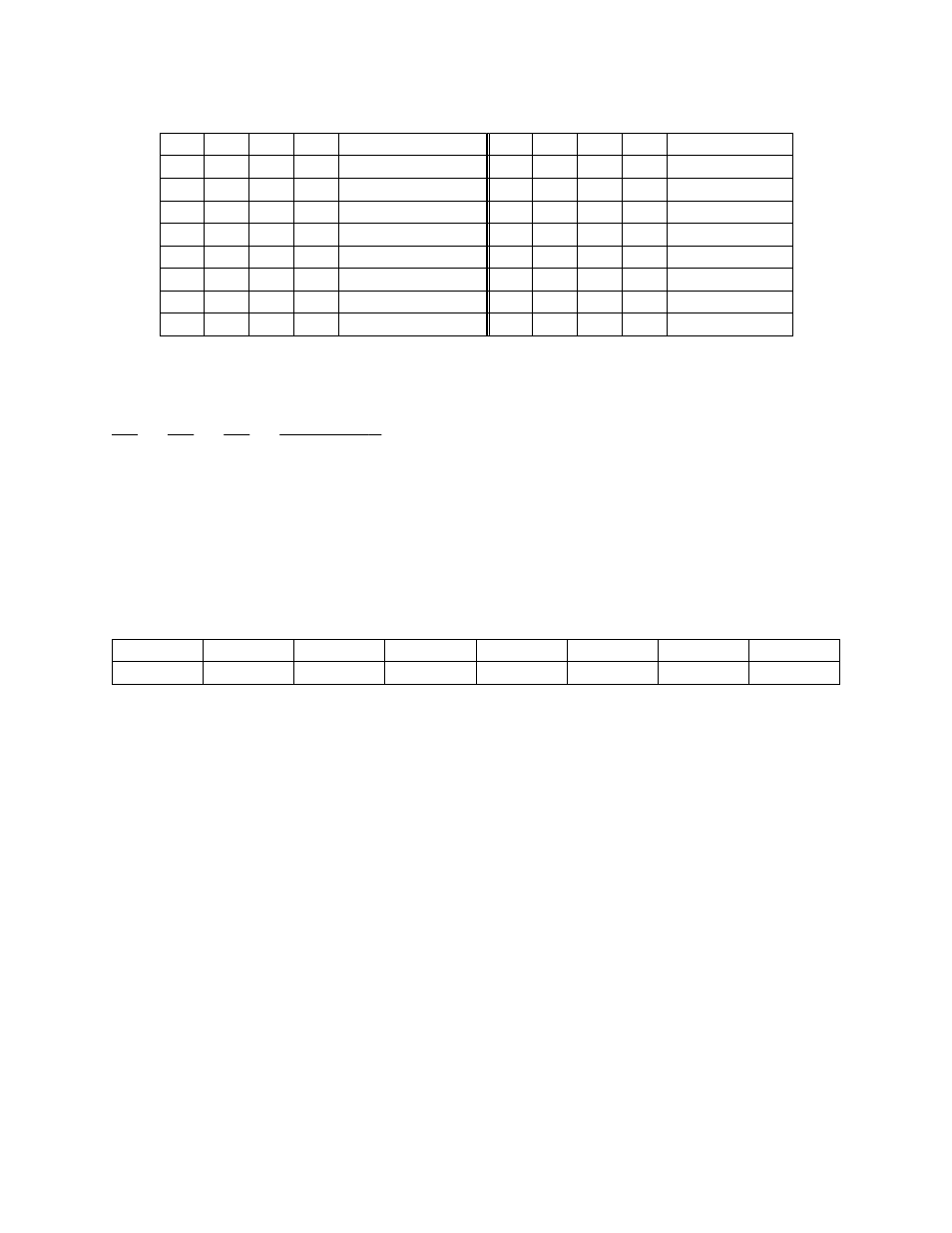

Table 5-2. Prescalar Divider/2 MHz Clock Control Codes

61.01

1

1

1

1

15,625

1

1

1

0

122.07

0

1

1

1

31,250

0

1

1

0

244.14

1

0

1

1

62,500

1

0

1

0

488.28

0

0

1

1

125,000

0

0

1

0

976.56

1

1

0

1

250,000

1

1

0

0

1,953

0

1

0

1

500,000

0

1

0

0

3,906.25

1

0

0

1

None

1

0

0

0

7,812.5

0

0

0

1

None

0

0

0

0

Output Freq

P0

P1

P2

P3

Output Freq

P0

P1

P2

P3

When TMRE = 0, the Prescaler and Counter 2 are disabled. When TMRE = 1, the prescaler and Counter

2 are enabled.

IR2

IR1

IR0

Hardware IRQ

0

0

0

Disable interrupts

0

0

1

Disable interrupts

0

1

0

2

0

1

1

3

1

0

0

4

1

0

1

5

1

1

0

6

1

1

1

7

BASE + 5 Read - Read bit settings

IR0

IR1

IR2

TMRE

P0

P1

P2

P3

0

1

2

3

4

5

6

7

BASE + 6 Write - Load counter 0

A write to this address loads the v alue 65,535 into counter 0. T his must be done before trig gering a

conversion.

BASE + 7 Not used

12

Advertising