Pci-dio48h block diagram – Measurement Computing PCI-DIO48H User Manual

Page 8

Advertising

PCI-DIO48H User's Guide

Introducing the PCI-DIO48H

8

PCI-DIO48H block diagram

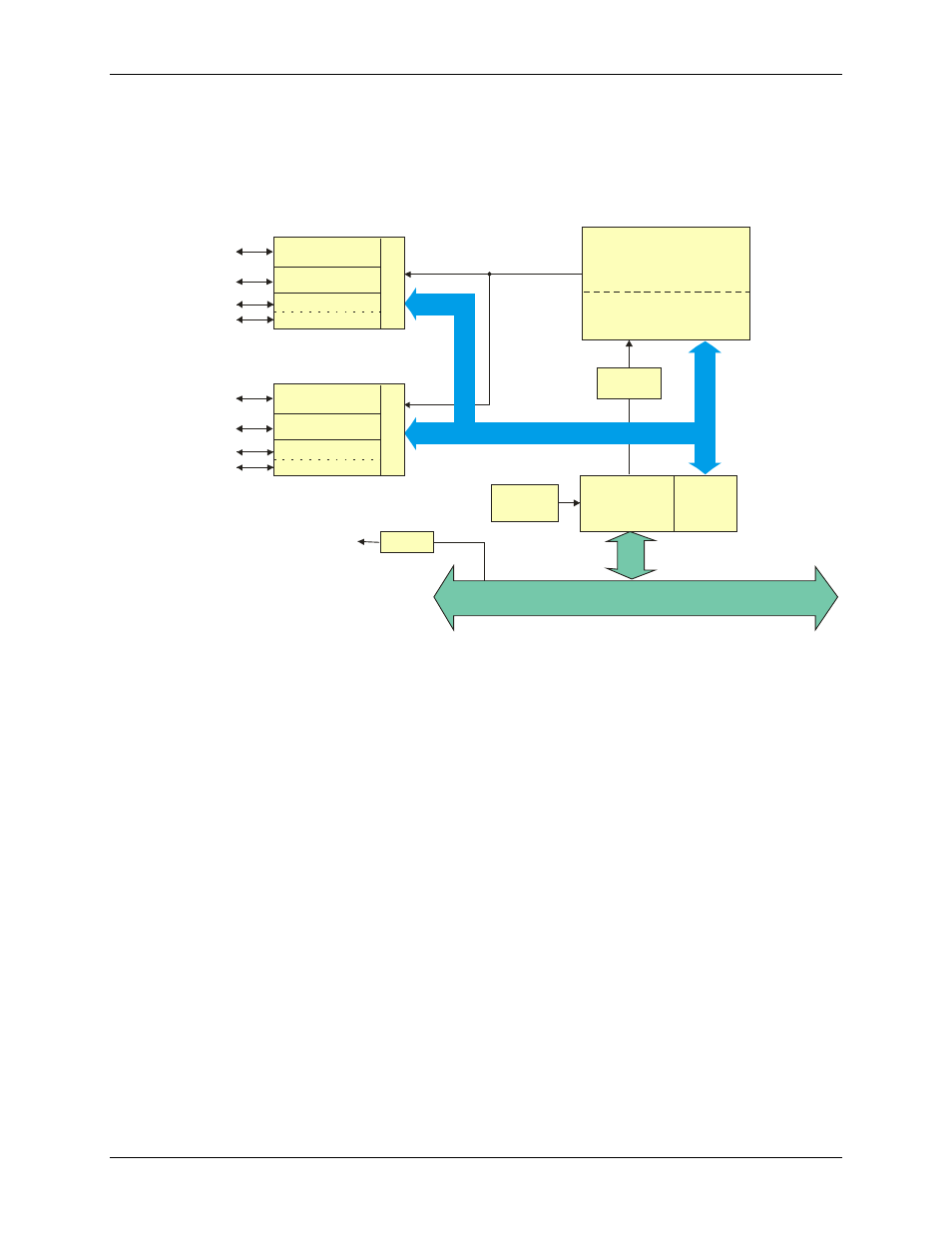

PCI-DIO48H functions are illustrated in the block diagram shown here.

PCI BUS (5V, 32-bit, 33 MHz)

PCI

Controller

BADR2

Boot

EEPROM

Control

Registers

Decode/Status

Controller CPLD and Logic

Local Bus

Control Bus

Bus

Timing

FIRSTPORTA

FIRSTPORTB

C

o

n

tr

o

l

FIRSTPORTCH

SECONDPORTA

SECONDPORT B

C

o

n

tr

o

l

HIGH DRIVE

SECONDPORT

FIRSTPORTA(7:0)

FIRSTPORTB(7:0)

FIRSTPORTCH(3:0)

FIRSTPORTCL(3:0)

FIRSTPORTCL

SECONDPORTA(7:0)

SECONDPORT B(7:0)

SECOND PORTCH(3:0)

SECONDPORTCL(3:0)

SECONDPORT CH

SECONDPORT CL

HIGH DRIVE

FIRSTPORT

Fuse

+5V User Output

+5V

Figure 1. PCI-DIO48H block diagram

Advertising