Altera LCD Multimedia HSMC User Manual

Page 13

2–5

Altera Corporation

LCD Multimedia HSMC

August 2008

Interface Device

The primary functions for this device are to

1.

Provide time-division multiplexing (TDM) functions to the LCD

and VGA color data bus.

2.

Provide level shifting feature for the 2.5V input (Cyclone III FPGA)

and 3.3V required by many of the interface chips.

This package has 272 user I/Os and comes in a 324-pin Fine-Line BGA

package.

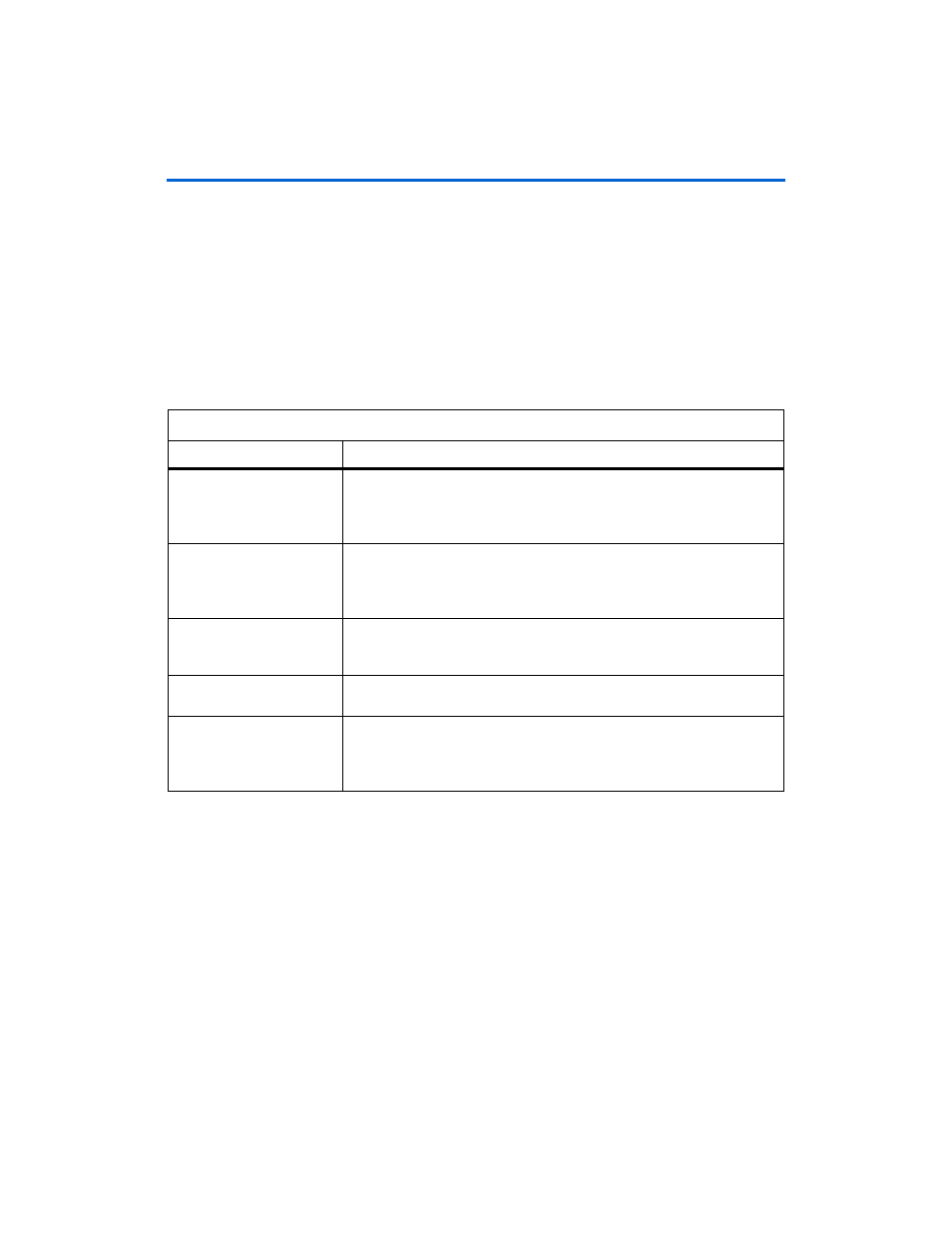

Table 2–3

lists Max II device features.

Table 2–3. Max II Device Features

Architectural Feature

Results

Altera’s second generation

low-cost CPLDs

●

Low cost packaging

●

Large number of logic elements

●

LUT based architecture

●

Fastest CPLD supports up to 300MHz clock frequency

Lowest power

consumption CPLD

●

Power down capability that conserves the battery life

●

Lowest dynamic power

●

Hot-socketing support

●

Single power supply simplicity

On-chip

user Flash memory

●

8kbit user accessible flash memory

●

Enables the integration of discrete and non-volatile storage

reducing chip count and cost

Real time In-signal

programmability

●

Capable of downloading a second design while the device is

operational

I/O capabilities

●

Supports interfacing with 1.8V, 2.5V and 3.3V logic levels of the

device due to Multivolt I/O capability

●

Schmitt triggers, programmable slew rate & programmable drive

strength improve signal integrity