Fpga registers – Artesyn iVPX7225 Installation and Use (April 2015) User Manual

Page 159

FPGA Registers

iVPX7225 Installation and Use (6806800S11C)

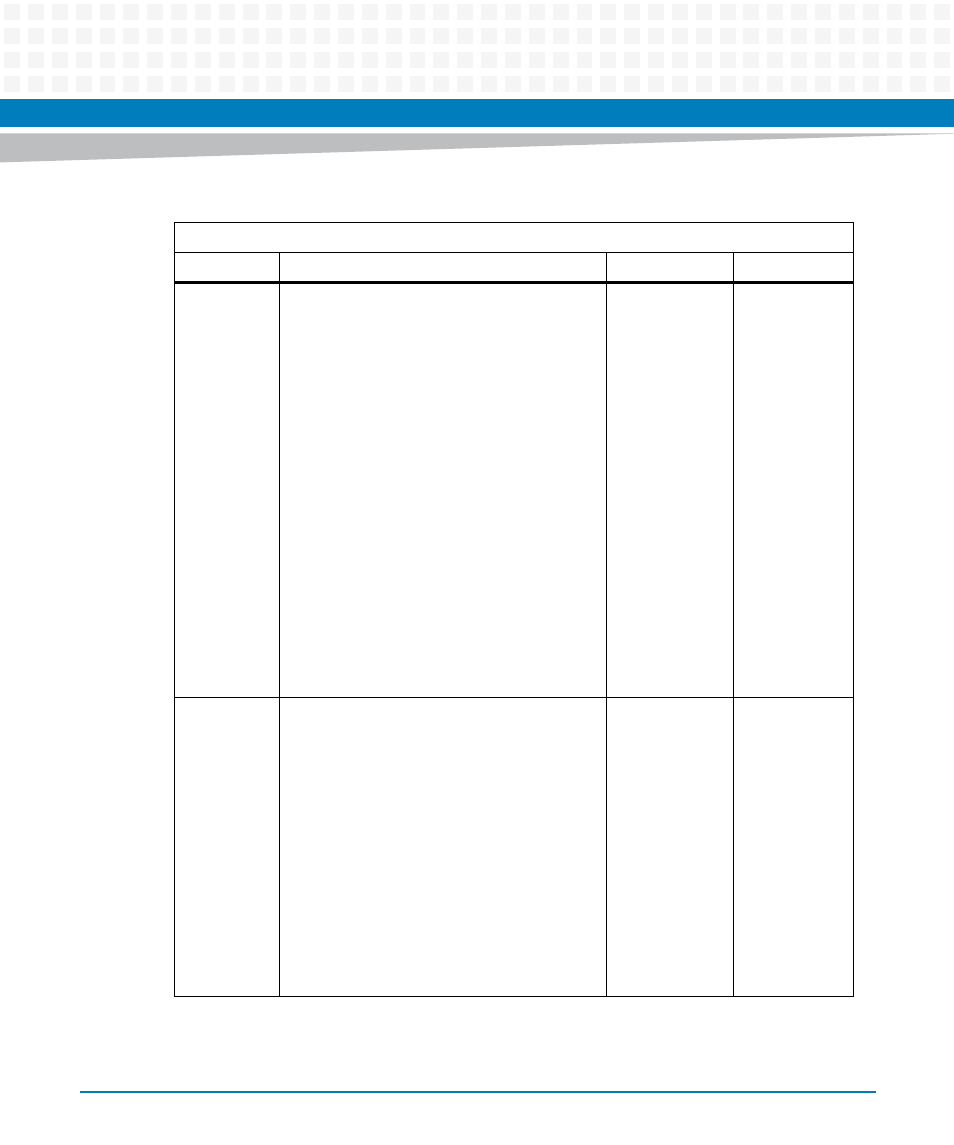

140

4

Break Interrupt (BI) indicator

When BI is set, it indicates that the received

data input was held low for longer than a full-

word transmission time. A full-word

transmission time is defined as the total time

to transmit the start, data, parity, and stop

bits. BI is cleared every time the CPU reads the

contents of the LSR. In the FIFO mode, this

error is associated with the particular

character in the FIFO to which it applies. This

error is revealed to the CPU when its

associated character is at the top of the FIFO.

When a break occurs, only one 0 character is

loaded into the FIFO. The next character

transfer is enabled after RXD goes to the

marking state for at least two Receiver CLK

samples and then receives the next valid start

bit:

1: Full WORD transmission time exceeded

0: Normal operation

0

R

5

Transmit Holding Register Empty (THRE)

indicator

THRE is set when the THR is empty, indicating

that the ACE is ready to accept a new

character. If the THRE interrupt is enabled

when THRE is set, an interrupt is generated.

THRE is set when the contents of the THR are

transferred to the TSR. THRE is cleared

concurrent with the loading of the THR by the

CPU. In the FIFO mode, THRE is set when the

transmit FIFO is empty; it is cleared when at

least one byte is written to the transmit FIFO:

1: THR/Transmit FIFO empty

0: THR/Transmit FIFO contains data

1

R

Table 7-53 Line Status Register (LSR) (continued)

IO Address: Base +5

Bit #

Description

Default

Access