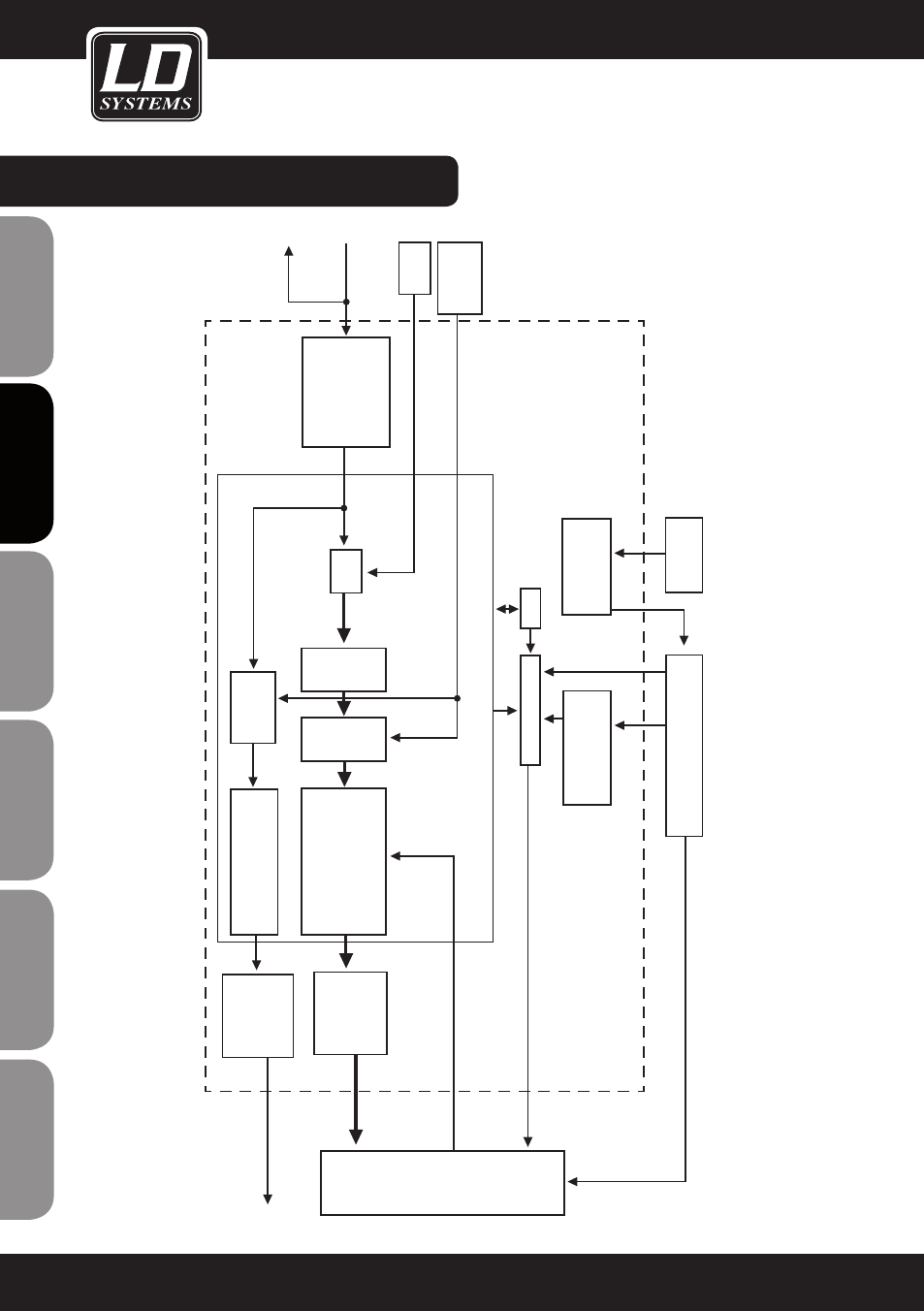

Dsp block diagramm – LD Systems DDQ 15 User Manual

Page 28

Advertising

ENGLISH

DEUTSCH

FRANCAIS

FRANCAIS

FRANCAIS

FRANCAIS

FRANCAIS

ESP

AÑOL

POLSKI

IT

ALIANO

28

Hea

t Sink

SIMPS

A

mp P

ow

er R

ail

Po

w

er

A

mps

2x

700W

Sub

w

oof

er

out S

ym.

Clip D

et

ec

t

Am

p

Lo

w C

ut/

Sub O

ut

G

ain

Enc

oder

A

nalog I

n

Sym.

A

nalog

link

Stacked ADC

24bit/48kH

z

Sens

. 23dBu

D

yn. 127dB

M

ast

er

G

ain

2 Ch.

2 C

h.

G

ain

D

ela

y

IlR EQ

IlR X

ov

Phase

2 C

h.

H

igh

Pass

2 C

h.

LS P

eak L

ook ahead (1ms)

LS T

her

mal

limit

er

A

mp RMS

1 C

h.

LS P

eak L

ook ahead (1ms)

1 C

h.

Lo

w

Pass

2 Ch D

AC

max L

ev

el

13,7dBu

113dB D

yn.

1 Ch D

AC

max L

ev

el

18dBu

113dB D

yn.

Limit

er D

ecr

ease

Shar

c

M

ut

e C

on

tr

ol

Onboar

d PS

+/- 14,4V Dig

Vol

.

Temp

. Ctr

.

µC

DSP BLOCK DIAGRAMM:

Advertising

This manual is related to the following products: