Sensoray 2600 User Manual

Page 57

Sensoray 2600 Programming Guide

53

Gateway Action Scheduling

The

mode

value is a collection of bit flags:

Returns:

Error code as described in section 5.5. Zero is returned if the operation was successful.

Benchmark: 0.9 ms.

Notes:

This function may be used to establish any arbitrary operating mode for a counter channel. It is provided so that

applications can tailor the counter operating mode in cases where the other mode setting functions, such as

S26_Sched2620_SetModeFreqMeas()

, do not provide sufficient control over counter operating parameters.

The new mode should be invoked by calling

S26_Sched2620_SetMode()

with the

RUN

flag negated so that the

counter will halt while the mode is being changed; this guarantees that the channel will be properly initialized

regardless of the physical state of its I/O pins.

S26_Sched2620_SetMode()

should then be called again with

RUN

asserted to enable the counter channel to run in the new mode.

Example:

// Set counter 3 operating mode to 0x0001 on the 2620 at MM number 0, IOM port 12.

void *x = S26_SchedOpen( 0, 1 );

S26_Sched2620_SetMode( x, 12, 3, 0x0001 );

// Halt channel and set mode.

S26_Sched2620_SetMode( x, 12, 3, 0x1001 );

// Run in the new mode.

S26_SchedExecute( x, 1000, 0 );

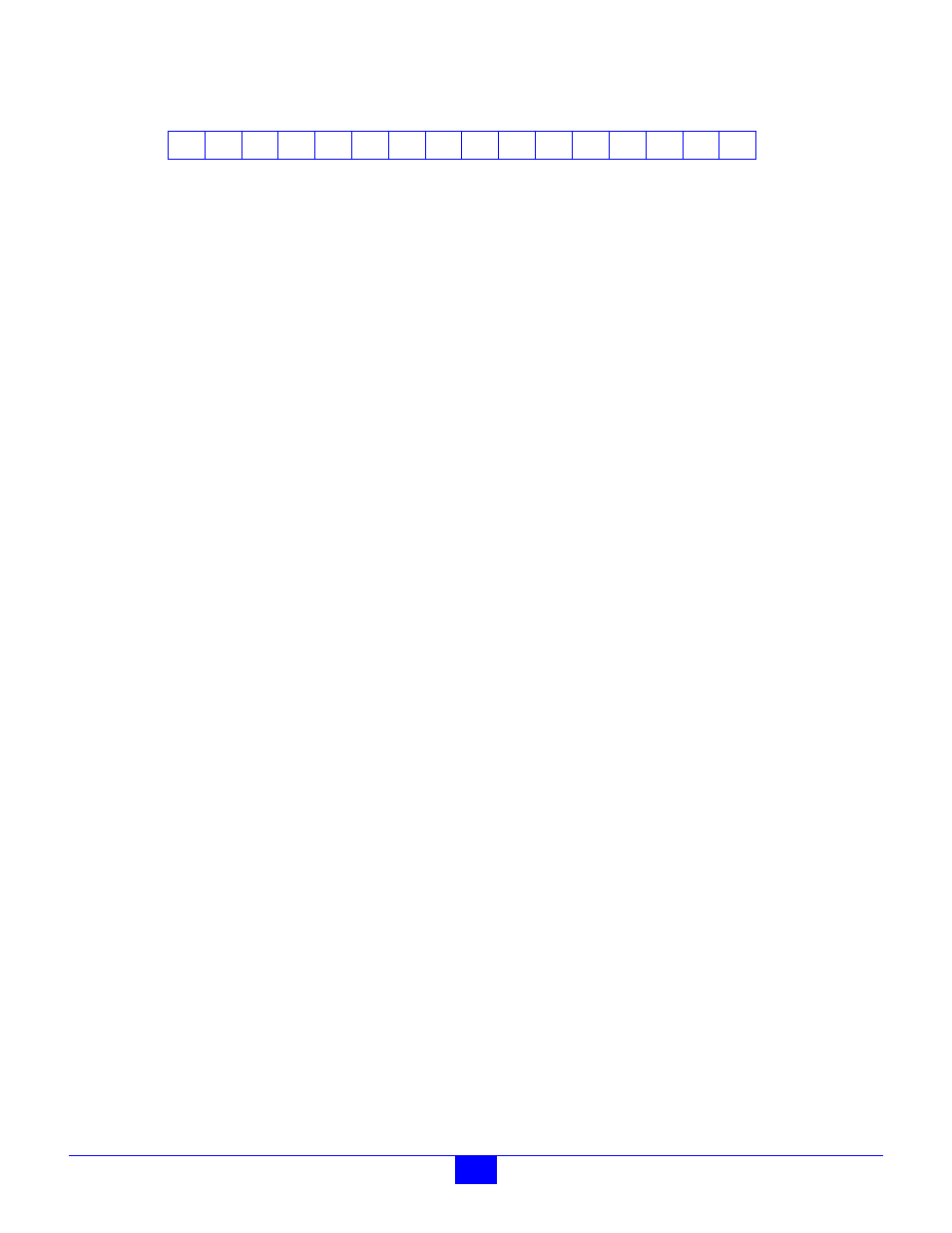

15

RUN

14

OM1

13

OM0

12

XP

11

PL1

10

PL0

9

LAT

8

CET

7

OP

6

M2

5

M1

4

M0

3

CD1

2

CD0

1

PLM

0

XC

RUN: Enable channel operations.

0 - (default upon module reset) Halt channel, force core to

zero (including bit 32), force status bits to their default

states, reset trigger latches. Preload and latch registers

are not modified. After writing to the mode register

with this bit cleared, it is necessary to write to it again

with this bit set to start the channel running.

1 - Run or continue to run in the specified mode.

OM: Output pin’s mode (2-bit field):

0 - Counter bit 31.

1 - Counter bit 32 (toggles at zero counts).

2 - Active when counts are zero.

3 - Active during counter under/overflow.

XP: Index input polarity:

0 - Active high.

1 - Active low.

PL: Preload trigger (2-bit field):

0 - Preload on soft trigger only.

1 - Preload on index leading edge or soft trigger.

2 - Preload on zero counts reached or soft trigger.

3 - Reserved.

LAT: Latch trigger:

0 - Latch on soft trigger only.

1 - Latch on index leading edge or soft trigger.

CET: Count enable trigger:

0 - Enable upon configuration (no trig needed).

1 - Enable on index leading edge.

OP: Output pin’s polarity:

0 - Active high.

1 - Active low.

M: Mode (3-bit field). Modes 0-3 use quadrature-encoded

two-phase clock, modes 4-6 use single-phase clock, and

mode 7 uses the internal clock:

0 - quad x1, clock on rising A.

1 - quad x1, clock on falling A.

2 - quad x2, clock on either edge of A.

3 - quad x4, clock on either edge of A or B.

4 - mono, clock on rising A, B controls count direction.

5 - mono, clock on falling A, B controls count direction.

6 - mono, clock on either edge A, B controls count

direction.

7 - internal clock (10MHz), A is the gate (enables

counting while asserted), B controls count direction.

CD: Count disable trigger:

0 - Never disabled by any trigger.

1 - Disable on index trailing edge (if enabled).

2 - Disable when zero counts reached.

PLM: Select preload register:

0 - Only preload register 0.

1 - Use both preload registers.

XC: Index source:

0 - External Index pin.

1 - Internal free-running gate generator.