B.30 status:questionable:enable command, B.31 status:questionable:enable? query, B.32 status:questionable:instrument? query – KEPCO MBT Series User Manual

Page 141: Table b-4. questionable instrument register 0 bits, B.33 status:questionable:instrument1? query, B.30, Stat, B.31, B.32, B.33

MBTSVC 111609

B-9

B.30 STATus:QUEStionable:ENABle COMMAND

STAT:QUES:ENAB

Syntax:

Short Form: STAT:QUES:ENAB <int_value> Long Form: STATus:QUESionable:ENABle <int_value>

Description: Programs Questionable Condition Enable Register (see Table B-3).The Questionable Condition

Enable Register determines which conditions are allowed to set the Questionable Condition Register;

it is a mask for enabling

specific bits in the Questionable Event register that can cause the question-

able summary bit (bit 3) of the Status Byte register to be set. The questionable summary bit is the log-

ical OR of all the enabled bits in the Questionable Event register

.

Bit set to 1 = function enabled

(active, true); bit reset to 0 = function disabled (inactive, false)

.

(See example, Figure B-5.)

B.31 STATus:QUEStionable:ENABle? QUERY

STAT:QUES:ENAB?

Syntax:

Short Form: STAT:QUES:ENAB? Long Form: STATus:QUESionable:ENABle?

Return Value: <int_value> actual register value

Description: Reads Questionable Condition Enable Register (see Table B-3). Power supply returns value of

Questionable Condition Enable Register, indicating which conditions are being monitored. Bit set to 1

= function enabled (active, true); bit reset to 0 = function disabled (inactive, false)

.

Related Com-

mands: STAT:QUES?. (See example, Figure B-5.)

B.32 STATus:QUEStionable:INSTrument? QUERY

STAT:QUES:INST?

Syntax:

Short Form: STAT:QUES:INST? Long Form: STATus:QUESionable:INSTrument?

Return Value: <int_value> actual register value

Description: Reads Questionable Instrument Register 0 (see Table B-4). Unit returns value of Instrument Regis-

ter 0 (inst register). The bits of this register are set when at leat one bit in the specified channel’s ISUM

register was set previously and the specific enable bit was also set. When this register is read, bits 1 -

14 are cleared. Bit 0 which indcates the summary of the bits in Instrument Register 1 (inst1 register)

remains set until the inst1 register is read.

B.33 STATus:QUEStionable:INSTrument1? QUERY

STAT:QUES:INST1?

Syntax:

Short Form: STAT:QUES:INST1? Long Form: STATus:QUESionable:INSTrument1?

Return Value: <int_value> actual register value

Description: Reads Questionable Instrument Register 1 (see Table B-5). Unit returns value of Instrument Regis-

ter 1 (inst1 register). The bits of this register are set when at leat one bit in the specified channel’s

ISUM register was set previously and the specific enable bit was also set. When this register is read,

bits 1 - 14 are cleared. Bit 0 which indcates the summary of the bits in Instrument Register 2 (inst2 reg-

ister)

remains set until the inst2 register is read.

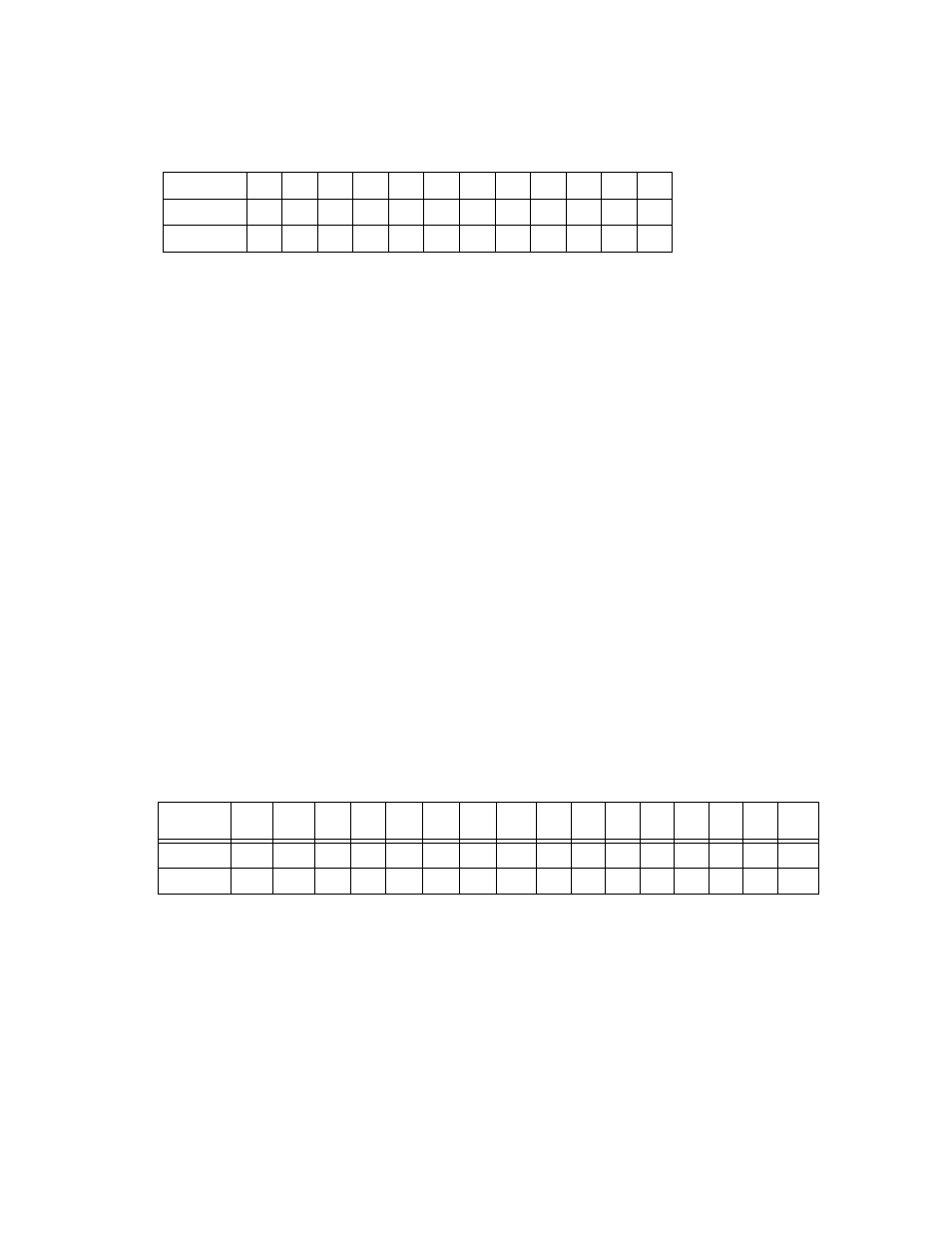

TABLE B-3. QUESTIONABLE EVENT REGISTER, QUESTIONABLE CONDITION REGISTER

AND QUESTIONABLE CONDITION ENABLE REGISTER BITS

CONDITION

PL

OL

RE

NU

NU

NU

NU

NU

OT

NU

CE

VE

BIT

11

10

9

8

7

6

5

4

3

2

1

0

VALUE

2048 1024

512

256

128

64

32

16

8

4

2

1

PL

POWER LOSS

OL

OVERLOAD

RE

RELAY ERROR

OT

OVERTEMPERATURE

CE

CURRENT ERROR

VE

VOLTAGE ERROR

NU

NOT USED

TABLE B-4. QUESTIONABLE INSTRUMENT REGISTER 0 BITS

CONDITION

NU

CH

14

CH

13

CH

12

CH

11

CH

10

CH

9

CH

8

CH

7

CH

6

CH

5

CH

4

CH

3

CH

2

CH

1

INST1

BIT

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

VALUE

32768 16384 8192 4096 2048

1024

512

256

128

64

32

16

8

4

2

1

CH

CHANNEL

NU

NOT USED

INST1 INSTRUMENT REGISTER 1