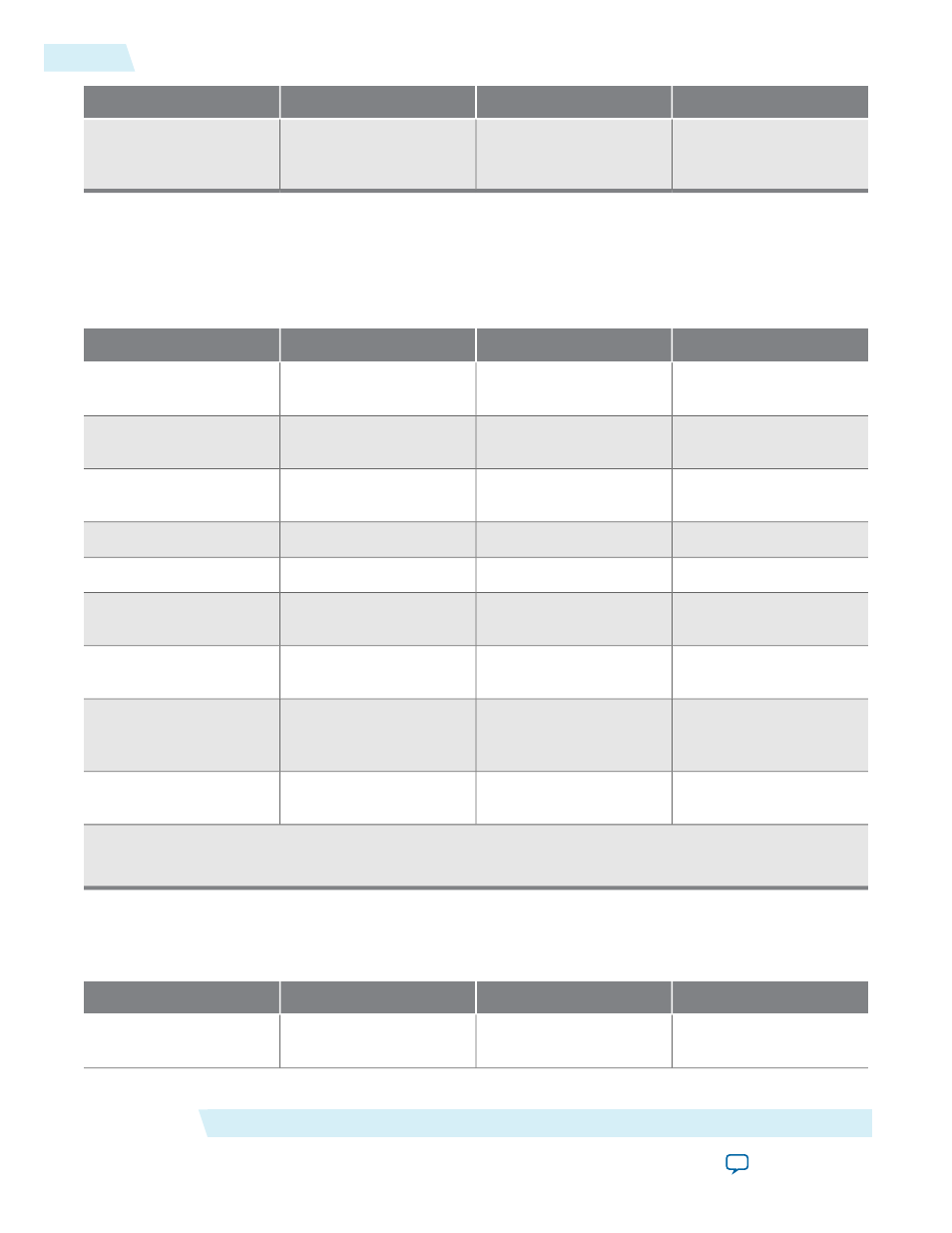

Altufm_none ports, Input ports, Output ports – Altera User Flash Memory User Manual

Page 32

Comments

Description

Required

Port Name

Data input from master

and data output from

slave.

Bidirectional clock port.

Yes

sda

ALTUFM_NONE Ports

Input Ports

Table 29: ALTUFM_NONE Input Ports

Comments

Description

Required

Port Name

(1)

Clock for the address

register

Yes

arclk

(1)

Input for the address

register.

Yes

ardin

(1)

Shift signal for the address

register.

Yes

arshft

(1)

Clock for the data register.

Yes

drclk

(1)

Input for the data register.

Yes

drdin

(1)

Shift signal for the data

register.

Yes

drshft

(1)

Signal that controls the

erase sequence.

Yes

erase

If the osc port is

specified, the oscena

port is required.

(1)

Signal that enables the

internal oscillator.

No

oscena

(1)

Signal that initiates a

program sequence.

No

program

Note to Table 3–12:

1. This port is used without an interface protocol only.

Output Ports

Table 30: ALTUFM_NONE Output Ports

Comments

Description

Required

Port Name

(1)

Busy signal that indicates

when memory is busy.

Yes

busy

Altera User Flash Memory (ALTUFM) IP Core User Guide

Altera Corporation

UG-040105

ALTUFM_NONE Ports

32

2014.08.18