Altera Avalon Tri-State Conduit Components User Manual

Page 12

2–6

Chapter 2: Generic Tri-State Controller

Example Read and Write Using Setup, Hold and Wait Times

Avalon Tri-State Conduit Components User Guide

May 2011

Altera Corporation

Preliminary

Figure 2–2

illustrates the timing of reads and writes given parameter settings

specified in

Table 2–4

.

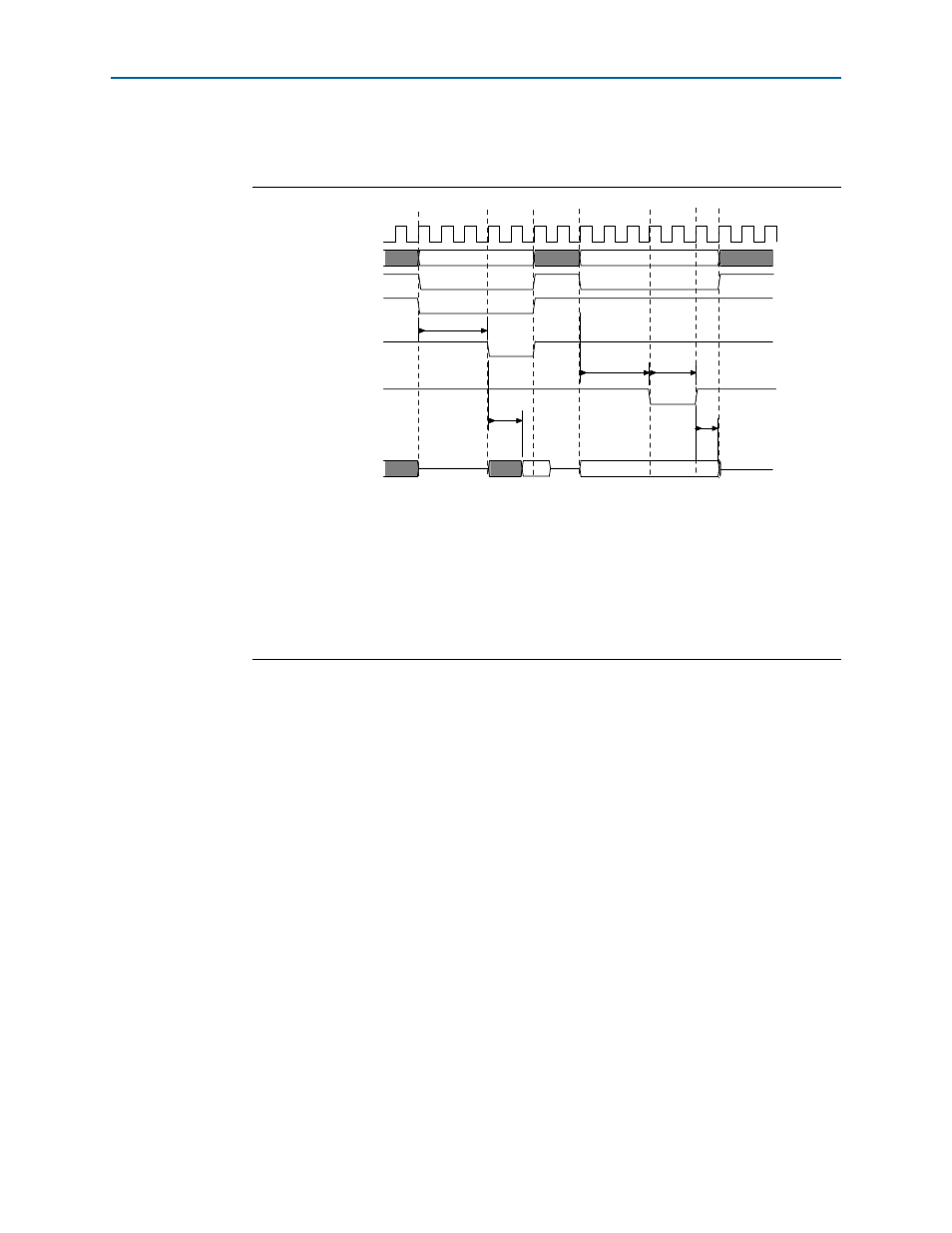

Figure 2–2. Read and Write Transfers with Setup Time and Wait States

Notes to

Figure 2–2

:

(1) The master drives

address

and asserts

chipselect_n

.

(2) After 3 cycles setup wait time, the interconnect asserts

read_n

.

(3) The slave port deasserts

read_n

after 2 cycles (from 30 ns) of read wait time. Data is sampled at the rising clock

edge.

(4)

address

and

writedata

are driven.

(5)

write_n

is driven after 3 cycles (from 50 ns) setup wait time.

(6)

write_n

is deasserted after two cycles (from 30 ns) of write wait time.

(7)

address

,

chipselect

, and the data bus stop being driven after 1 cycle (from 10 ns) of hold time.

clk

address

chipselect_n

outputenable_n

read_n

write_n

data

addr1

addr2

data

writedata

setup time

write wait time

read wait time

setup time

2

3

4

5

6

7

1

data hold time