Altera Arria V Avalon-ST User Manual

Page 92

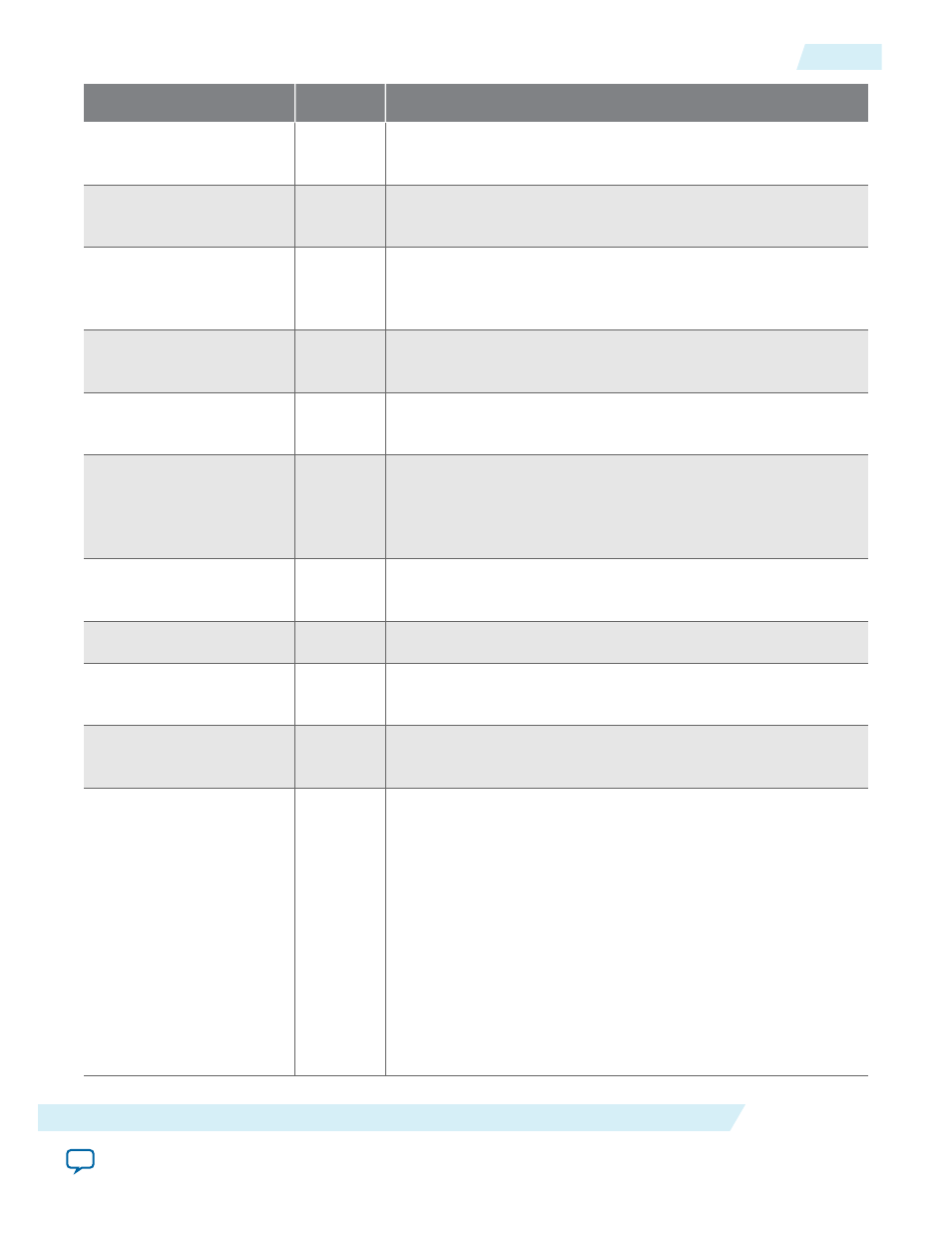

Signal

Direction

Description

txdetectrx0

Output

Transmit detect receive <n>. This signal tells the PHY layer to

start a receive detection operation or to begin loopback.

txelecidle0

Output

Transmit electrical idle <n>. This signal forces the TX output to

electrical idle.

txcompl0

Output

Transmit compliance <n>. This signal forces the running

disparity to negative in Compliance Mode (negative COM

character).

rxpolarity0

Output

Receive polarity <n>. This signal instructs the PHY layer to

invert the polarity of the 8B/10B receiver decoding block.

powerdown0[1:0]

Output

Power down <n>. This signal requests the PHY to change its

power state to the specified state (P0, P0s, P1, or P2).

tx_deemph0

Output

Transmit de-emphasis selection. The Arria V Hard IP for PCI

Express sets the value for this signal based on the indication

received from the other end of the link during the Training

Sequences (TS). You do not need to change this value.

rxdata0[7:0]

(1)

Input

Receive data <n> (2 symbols on lane <n>). This bus receives data

on lane <n>.

rxdatak0

(1)

Input

Receive data >n>. This bus receives data on lane <n>.

rxvalid0

(1)

Input

Receive valid <n>. This signal indicates symbol lock and valid

data on

rxdata

<n> and

rxdatak

<n>.

phystatus0

(1)

Input

PHY status <n>. This signal communicates completion of several

PHY requests.

eidleinfersel0[2:0]

Output

Electrical idle entry inference mechanism selection. The

following encodings are defined:

• 3'b0xx: Electrical Idle Inference not required in current

LTSSM state

• 3'b100: Absence of COM/SKP Ordered Set in the 128 us

window for Gen1 or Gen2

• 3'b101: Absence of TS1/TS2 Ordered Set in a 1280 UI interval

for Gen1 or Gen2

• 3'b110: Absence of Electrical Idle Exit in 2000 UI interval for

Gen1 and 16000 UI interval for Gen2

• 3'b111: Absence of Electrical idle exit in 128 us window for

Gen1

2014.12.15

PIPE Interface Signals

4-55

Interfaces and Signal Descriptions

Altera Corporation