Altera RAM-Based Shift Register User Manual

Page 18

2–12

Chapter 2: Getting Started

Design Example: Shift Register with Taps

RAM-Based Shift Register (ALTSHIFT_TAPS) Megafunction User Guide

May 2013

Altera Corporation

1

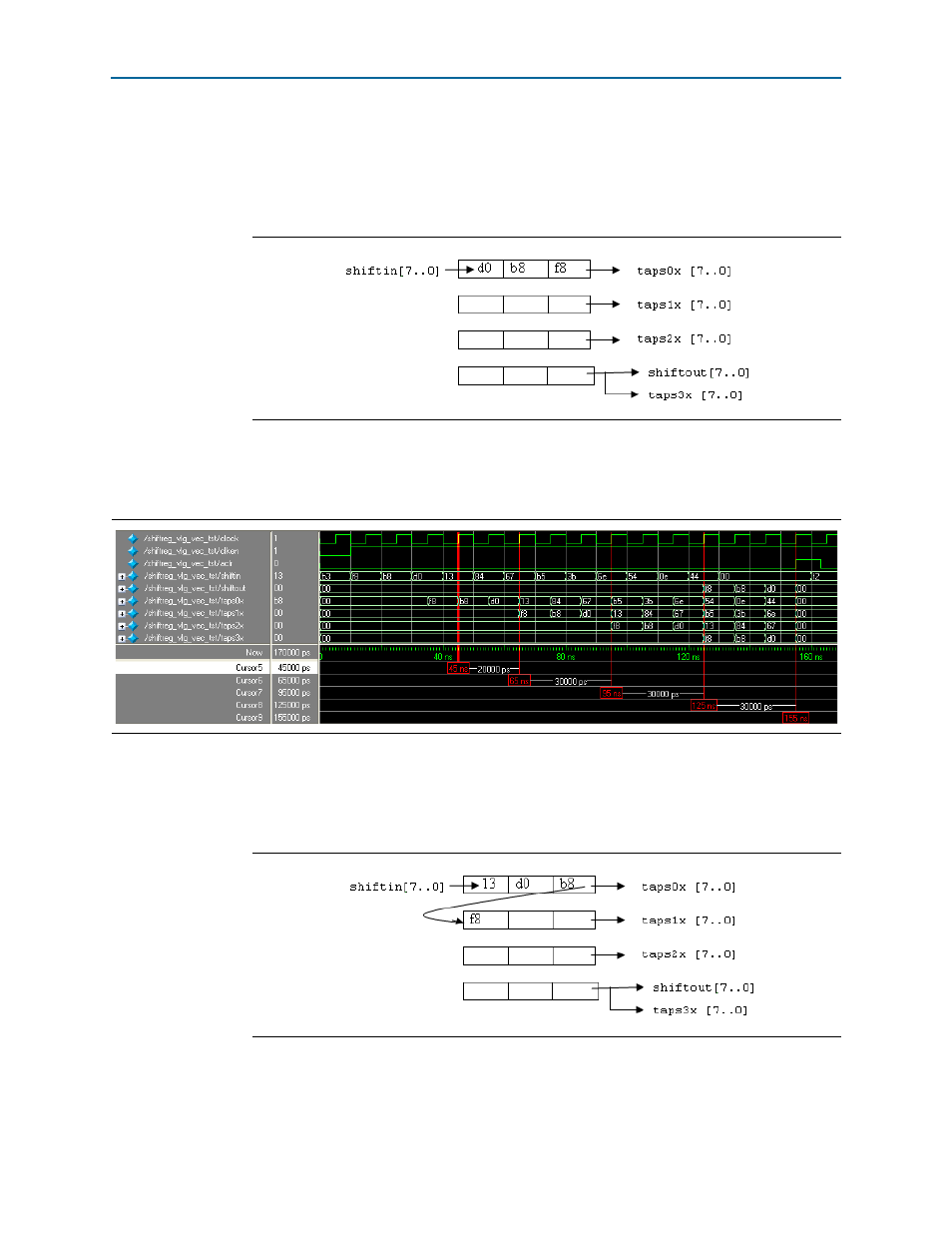

None of the input and output data ports are registered. Only the address ports of the

memory block within the shift register are registered. Therefore, when the data are

shifted to any of the output ports, the data are shown immediately at the respective

output ports.

shows the data-shifting and output-tapping from the shift register chain

at evenly-spaced intervals.

At 45 ns, the first data F8 is shifted to the next row of taps and the second data B8 is

shifted to taps0x, as shown in

. Other output ports continue to show 00.

Also, at the same rising clock edge, the new data 13 is shifted into the shift register.

Figure 2–11. Content of the Shift Register Chain at 35 ns

Figure 2–12. Data-Shifting and Output-Tapping

Figure 2–13. Content of the Shift Register Chain at 45 ns