Altera Active Serial Memory Interface User Manual

Page 11

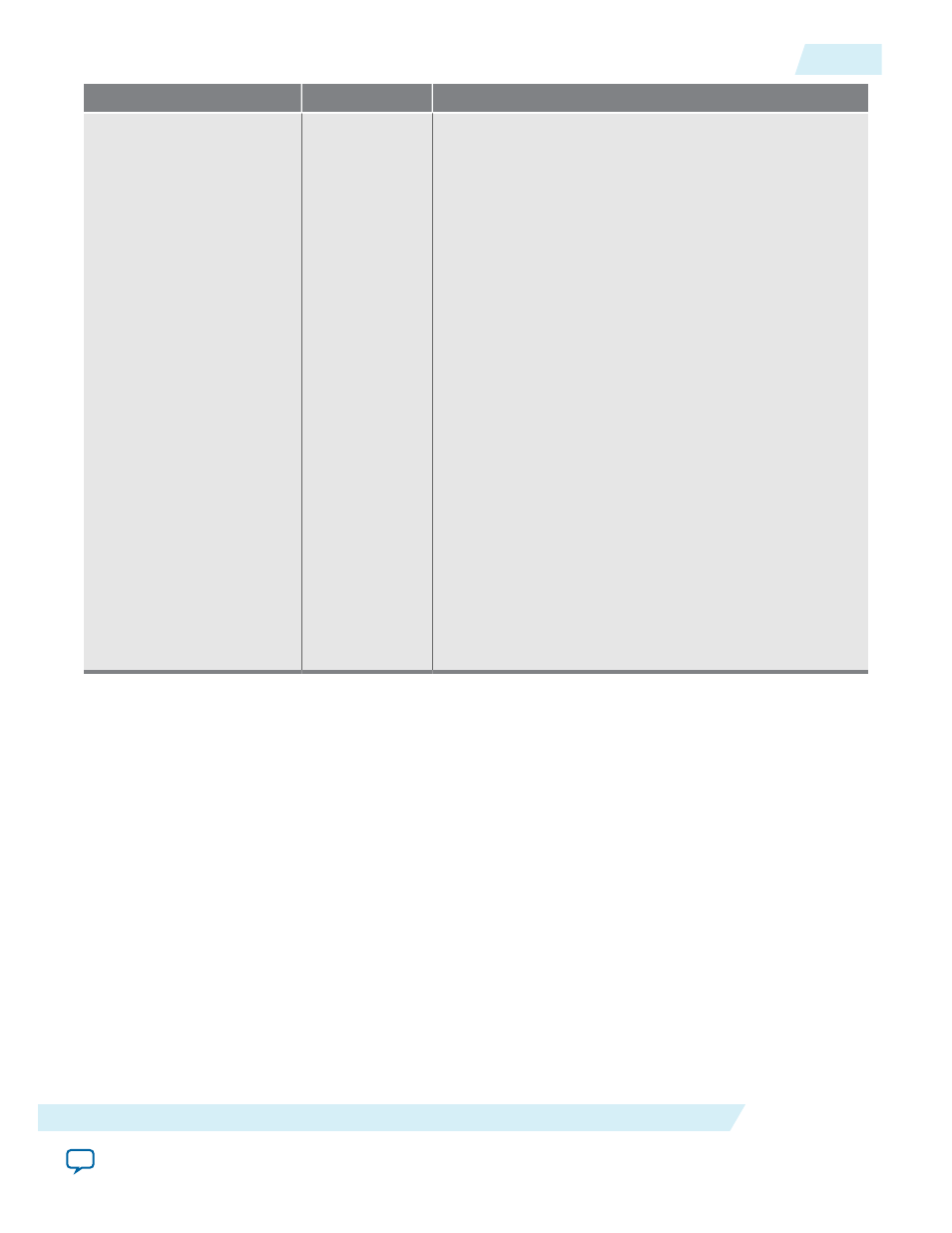

Parameter

Legal Values

Descriptions

Disable dedicated Active

Serial interface

—

• This option is disabled by default and the IP core

generates the design file as per usual.

• The Altera ASMI Parallel IP core instantiates the ASMI

block internally and connects to the block automati‐

cally.

• The IP core creates the following input/output pins

when you enable this option:

asmi_dataout

,

asmi_dclk

,

asmi_scein

,

asmi_sdoin

,

asmi_dataoe

.

• When you enable this option, the Altera ASMI Parallel

IP core will not instantiate ASMI block automatically,

and all signals to interface with ASMI block are routed

to the top level of your design. You must then

instantiate the ASMI block externally, and assign the

ASMI ports in the Altera ASMI Parallel IP core to the

dedicated pins location.

• The CLI parameter to disable this option is

USE_

ASMIBLOCK=ON.

• This option is available for all EPCS/EPCQ/EPCQ-L

devices.

Related Information

•

For more information about starting the IP Parameter Editor

•

Quad-Serial Configuration (EPCQ) Devices Datasheet

For the designated Altera ASMI Parallel dummy cycles values

• on page 20

For more information about the Use ‘read_sid’ port parameter

• on page 29

For more information about the Use ‘read_status’ port parameter

• on page 19

For more information about the Use ‘read_rdid’ and ‘rdid_out’ ports parameter

• on page 26

For more information about the Enable write operation parameter

• on page 23

For more information about the Use ‘fast_read’ port parameter

• on page 21

For more information about the Use ‘sector_protect’ port parameter

UG-ALT1005

2014.12.15

Parameters

11

Altera ASMI Parallel IP Core User Guide

Altera Corporation