Altera 40-Gbps Ethernet MAC and PHY MegaCore Function User Manual

Page 175

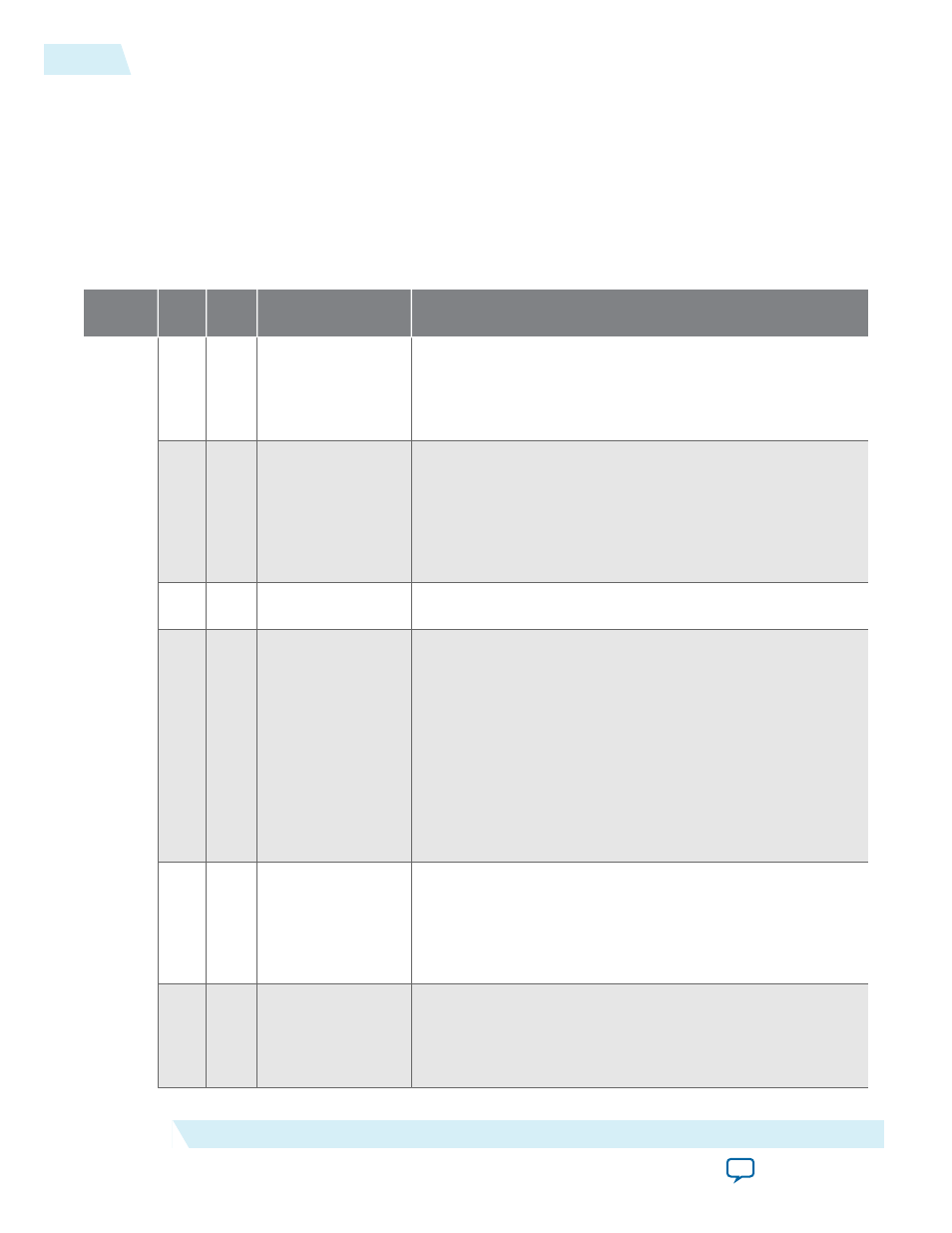

The following table specifies the control and status registers that you can access over the Avalon-MM

PHY management interface. A single address space provides access to all registers.

Notes:

• Unless otherwise indicated, the default value of all registers is 0.

• Writing to reserved or undefined register addresses may have undefined side effects.

• To avoid any unspecified bits to be erroneously overwritten, you must perform read-modify-writes to

change the register values.

Table C-1: 10GBASE-KR Register Definitions

Word

Addr

Bit

R/W

Name

Description

0xB0

0

RW

Reset SEQ

When set to 1, resets the 10GBASE-KR sequencer, initiates a

PCS reconfiguration, and may restart Auto-Negotiation, Link

Training or both if AN and LT are enabled (10GBASE-KR

mode). SEQ Force Mode[2:0] forces these modes. This reset

self clears.

1

RW

Disable AN Timer

Auto-Negotiation disable timer. If disabled (

Disable AN

Timer = 1

) , AN may get stuck and require software support

to remove the ABILITY_DETECT capability if the link

partner does not include this feature. In addition, software

may have to take the link out of loopback mode if the link is

stuck in the ACKNOWLEDGE_DETECT state. To enable

this timer set

Disable AN Timer = 0

.

2

RW

Disable LF Timer

When set to 1, disables the Link Fault timer. When set to 0,

the Link Fault timer is enabled.

6:4

RW

SEQ Force

Mode[2:0]

Forces the sequencer to a specific protocol. Must write the

Reset SEQ

bit to 1 for the Force to take effect. The following

encodings are defined:

• 3'b000: No force

• 3'b001: GigE

• 3'b010: Reserved

• 3'b011: Reserved

• 3'b100: 10GBASE-R

• 3'b101: 10GBASE-KR

• Others: Reserved

16

RW

Assert KR FEC

Ability

When set to 1, indicates that the FEC ability is supported.

This bit defaults to 1 if the Set FEC_ability bit on power up/

reset bit is on. For more information, refer to the FEC

variable

FEC_Enable

as defined in Clause 74.8.2 and

10GBASE-KR PMD control register bit (1.171.0) IEEE

802.3ap-2007.

17

RW

Enable KR FEC

Error Indication

When set to 1, the FEC module indicates errors to the 10G

PCS. For more information, refer to the KR FEC variable

FEC_enable_Error_to_PCS

and 10GBASE-KR PMD control

register bit (1.171.1) as defined in Clause 74.8.3 of IEEE

302.3ap-2007.

C-2

10GBASE-KR PHY Register Definitions

UG-01088

2014.12.15

Altera Corporation

10GBASE-KR Registers