Altera DDR SDRAM Controller User Manual

Page 66

3–30

Chapter 3: Functional Description

Interfaces & Signals

DDR and DDR2 SDRAM Controller Compiler User Guide

© March 2009

Altera Corporation

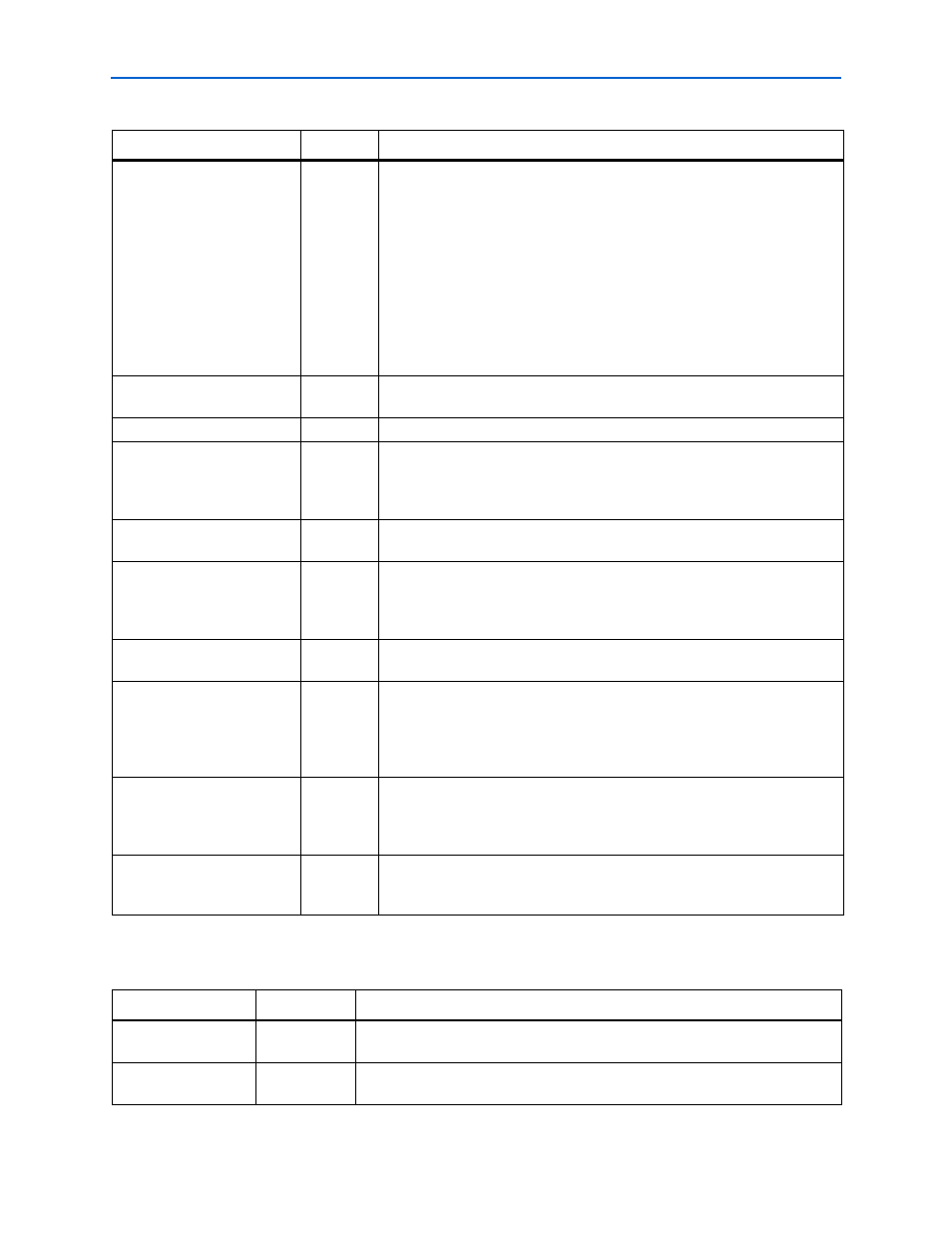

shows the DDR and DDR2 SDRAM interface signals.

local_size[]

Input

The burst size of the requested access, which is encoded as a binary number.

The controller supports maximum local burst lengths of 1, 2, or 4, for DDR

SDRAM; and 2 for DDR2 SDRAM.

You may request any size up to the maximum burst length, so for example if

you chose a memory burst length of 8, the local burst size is 4 and you may

request local bursts of length 1, 2, 3 or 4. Similarly, if you chose a memory

burst length of 4, the local burst length is 2 and you may request local bursts

of length 1 or 2.

If you chose a memory burst length of 2 (local burst length of 1), the

local_size[]

port is tied to 1 and is not visible on the controller interface.

For all other memory burst lengths, local_size is available.

local_wdata[]

Input

Write data bus. The width of local_wdata is twice that of the memory data

bus.

local_write_req

Input

Write request signal.

local_init_done

Output

Memory initialization complete signal, which is asserted once the controller

has completed its initialization of the memory. Read and write requests are still

accepted before local_init_done is asserted, however they are not

issued to the memory until it is safe to do so.

local_rdata[]

Output

Read data bus. The width of local_rdata is twice that of the memory data

bus.

local_rdata_valid

Output

Read data valid signal. The local_rdata_valid signal indicates that

valid data is present on the read data bus. The timing of

local_rdata_valid

is automatically adjusted to cope with your choice

of resynchronization and pipelining options.

local_rdvalid_in_n

Output

An early version of the read data valid signal which appears three cycles before

it. Not present in Avalon-MM mode.

local_ready

Output

The local_ready signal indicates that the DDR or DDR2 SDRAM

controller is ready to accept request signals. If local_ready is asserted in

the clock cycle that a read or write request is asserted, that request has been

accepted. The local_ready signal is deasserted to indicate that the DDR

or DDR2 SDRAM controller cannot accept any more requests.

local_refresh_ack

Output

Refresh request acknowledge, which is asserted for one clock cycle every time

a refresh is issued. Even if the User Controlled Refresh option is not selected,

local_refresh_ack

still indicates to the local interface that the

controller has just issued a refresh command.

local_wdata_req

Output

Write data request signal, which indicates to the local interface that it should

present valid write data on the next clock edge. Not present in Avalon-MM

mode.

Table 3–8. Local Interface Signals (Part 2 of 2)

Signal Name

Direction

Description

Table 3–9. DDR & DDR2 SDRAM Interface Signals (Part 1 of 2)

Signal Name

Direction

Description

ddr_dq[]

Bidirectional

Memory data bus. This bus is half the width of the local read and write data

busses.

ddr_dqs[]

Bidirectional

Memory data strobe signal, which writes data into the DDR or DDR2 SDRAM and

captures read data into the Altera device.