Altera Early SSN Estimator User Manual

Page 13

Chapter 2: Tutorial: Mixing SSTL and LVTTL in a Single Bank

2–3

© November 2009

Altera Corporation

Early SSN Estimator User Guide for Altera Programmable Devices

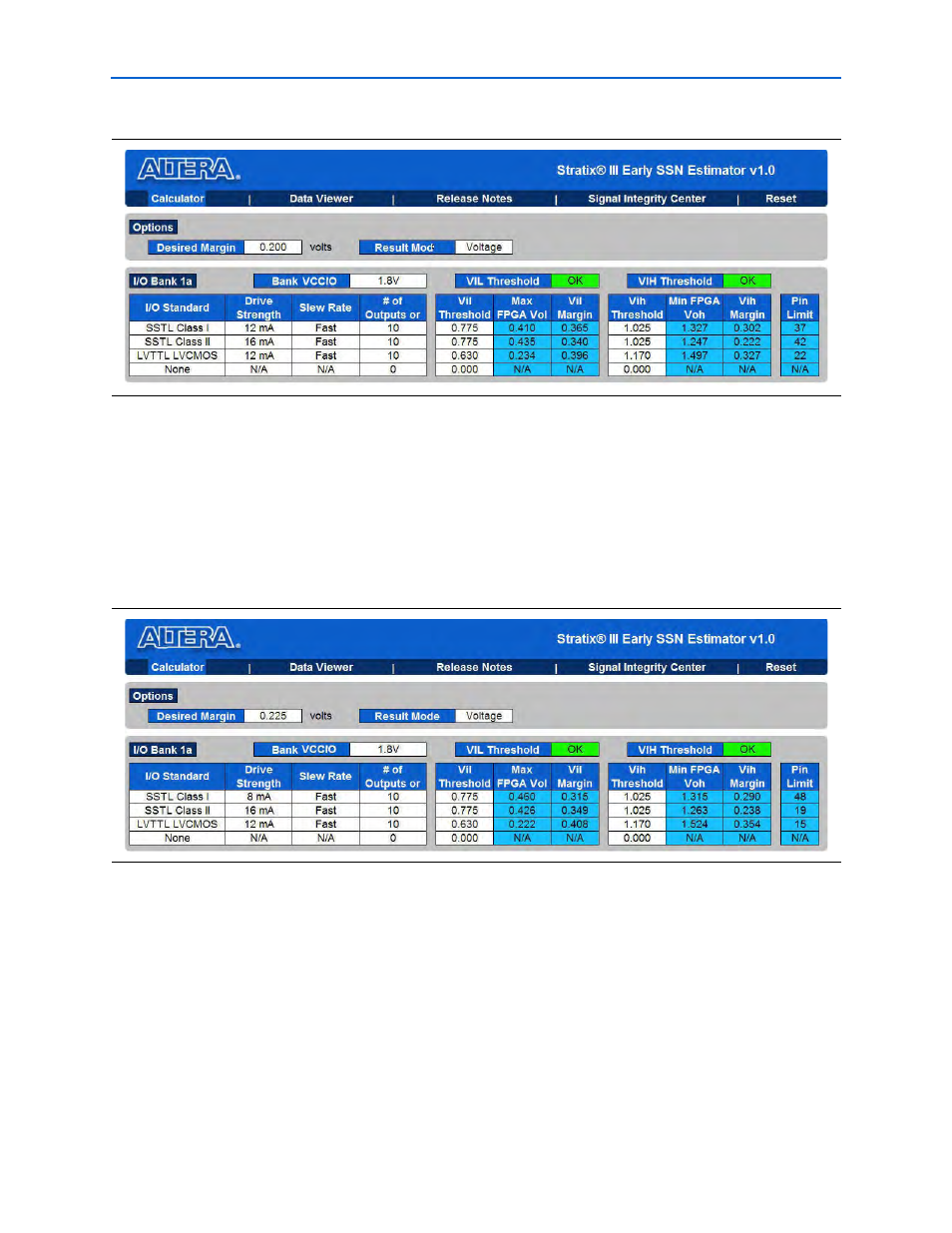

Second Approach

If the timing margin allows, reduce the current drive strength for the SSTL Class I

buffers from 12 mA to 8 mA, keeping the desired voltage margin at 225 mV for

non-SSN-related items, as shown in

This decrease in drive strength reduces the SSN sufficiently to allow you to

implement your design with ten SSTL Class I and ten SSTL Class II I/Os, along with

ten LVTTL I/Os with sufficient margin.

Third Approach

If the design allows, change the slew rate control SSTL Class I I/O to medium-fast,

keeping the desired voltage margin at 225 mV for non-SSN related items, as shown in

.

Changing the slew rate setting from fast to medium-fast reduces the SSN sufficiently

to allow you to implement your design with ten SSTL Class I and ten SSTL Class II

I/Os, along with ten LVTTL I/Os with sufficient margin.

1

Not all Altera device families have slew rate control option.

Figure 2–3. First Approach

Figure 2–4. Second Approach