Altera temperature sensor signals – Altera Temperature Sensor User Manual

Page 8

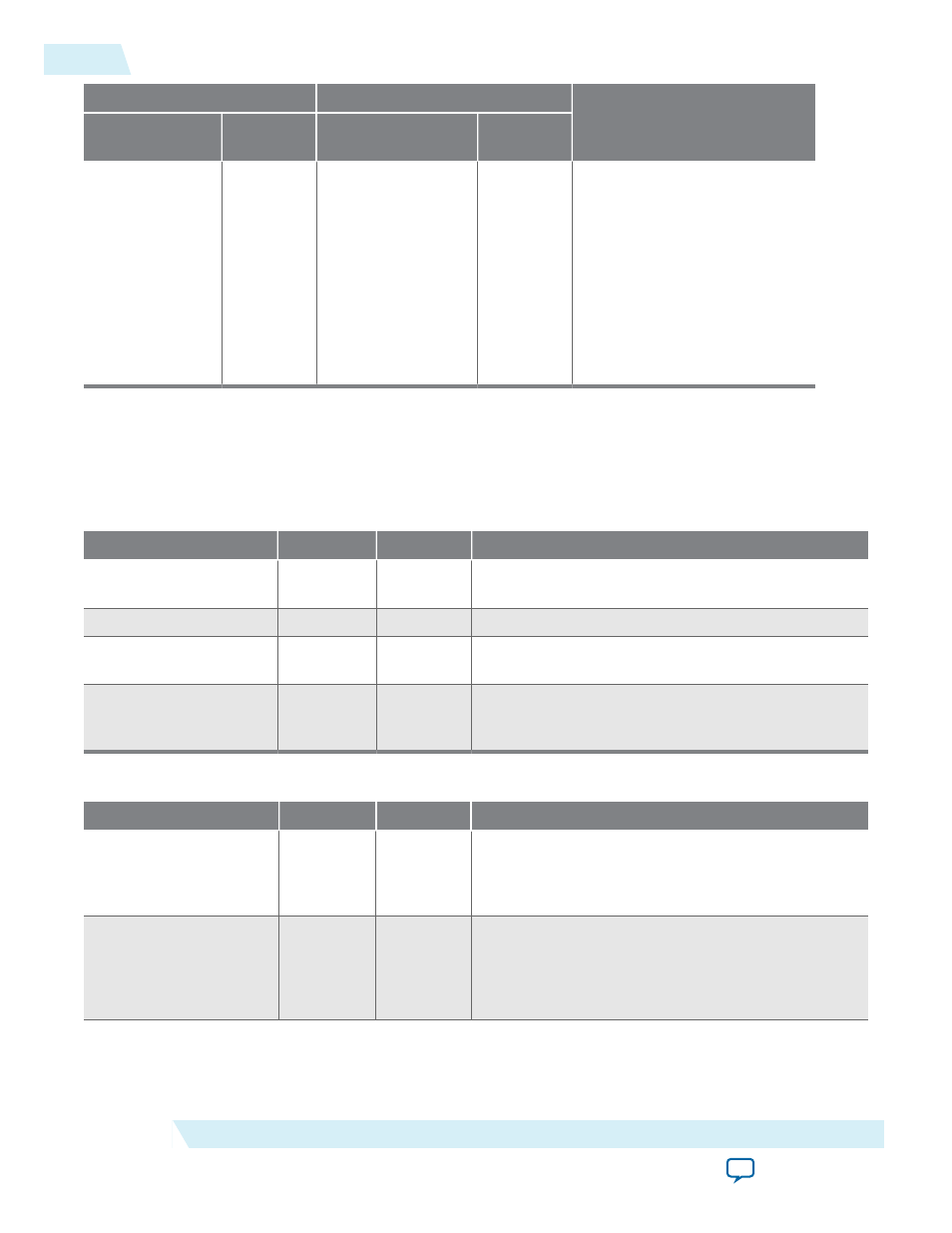

Parameter

CLI Parameter

Description

Name

Legal

Values

Name

Legal

Values

Create an

asynchronous

clear port

On/Off

clr

—

Specifies whether to turn on

the asynchronous clear (

clr

)

port.

Turn on this option when you

want to reset the Altera

Temperature Sensor IP core.

When you turn off this

option, the clear port

automatically connects to

GND.

Altera Temperature Sensor Signals

The following tables list the Altera Temperature Sensor IP core signals.

Table 4: Altera Temperature Sensor IP Core Signals for Arria 10 Devices

Signals

Direction

Width (Bit)

Description

corectl

Input

1

Enables the temperature sensing feature by the IP

core.

reset

Input

1

Resets the temperature sensing block.

tempout[9:0]

Output

10

10-bit output data from internal ADC circuitry of

temperature sensor block.

eoc

Output

1

Indicates end of internal ADC conversion. This

signal goes high for one clock cycles and you can

latch the data on

tempout

at the falling edge of EOC.

Table 5: Altera Temperature Sensor IP Core Signals for Suppported Devices

Signals

Direction

Width (Bit)

Description

clk

Input

1

Input clock signal that runs at a frequency of

80 MHz and below. The internal clock divider

reduces the frequency of the

clk

signal to 1 MHz or

less before clocking the ADC.

ce

Input

1

The asynchronous clock enable signal for the

clk

signal. This signal turns on/off the Altera Tempera‐

ture Sensor IP core that implements the TSD block.

This is an active-high signal. By default, this port

connects to VCC.

8

Altera Temperature Sensor Signals

UG-01074

2015.05.04

Altera Corporation

Altera Temperature Sensor IP Core User Guide