Write logic – Altera Virtual JTAG IP Core User Manual

Page 37

Functional Description

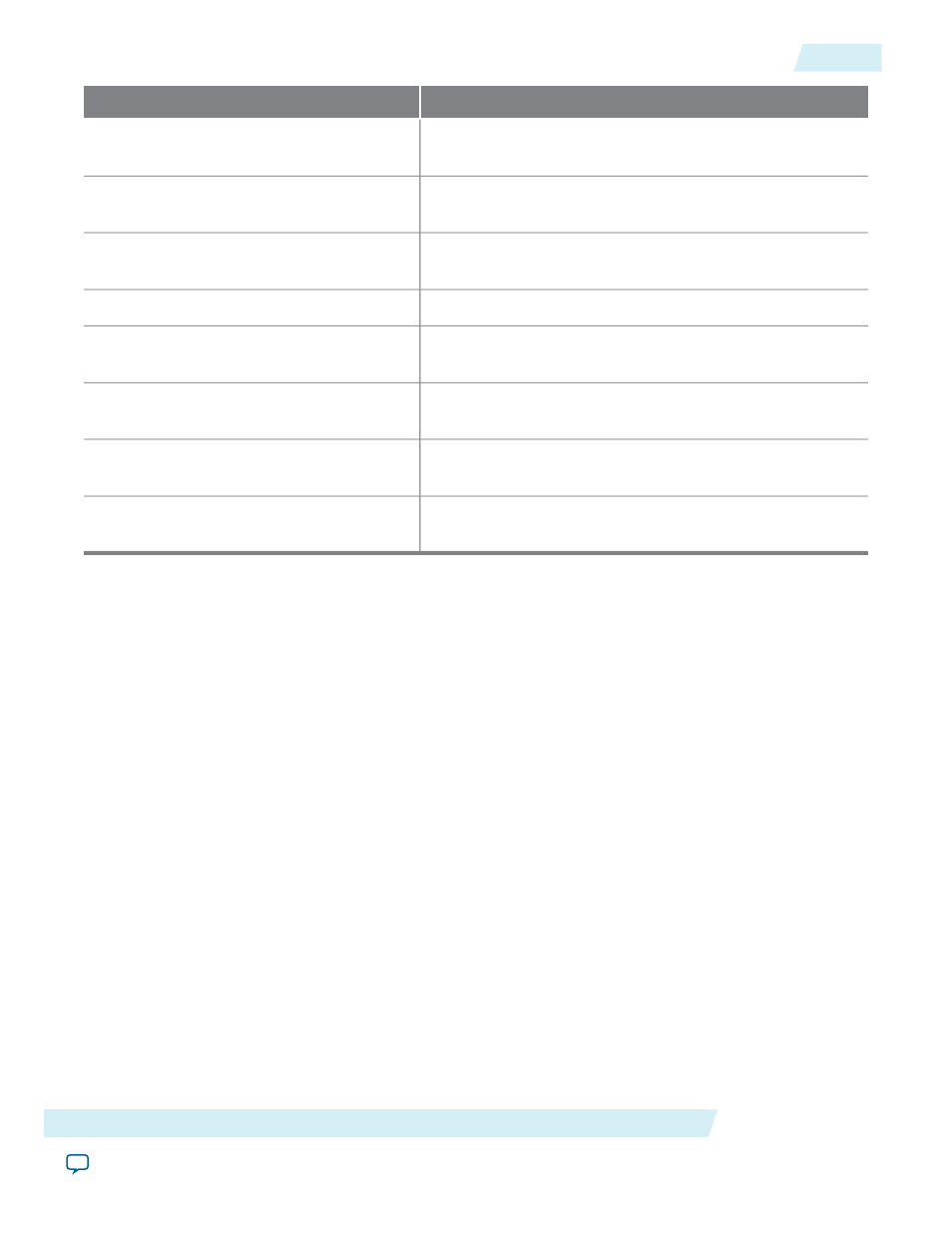

TAP Controller State

This is a hold state. Once entered, the controller remains in

this state as long as

TMS

is held low.

Run-Test/Idle

These are temporary controller states. A decision is made here

whether to enter the DR states or the IR states.

Select DR-Scan/Select IR Scan

These states enable a parallel load of the shift registers from

the hold registers on the rising edge of

TCK

.

Capture DR/Capture IR

These states enable shifting of the DR and IR chains.

Shift DR/Shift IR

Temporary hold states. A decision is made in these states to

either advance to the Update states or the Pause states.

Exit1 DR/Exit1 IR

This controller state allows shifting of the Instruction Register

and Data Register to be temporarily halted.

Pause DR/Pause IR

Temporary hold states. A decision is made in these states to

advance to the Update states.

Exit2 DR/Exit2 IR

These states enable a parallel load of the hold registers from

the shift registers. Update happens on the falling edge of

TCK

.

Update DR/Update IR

Design Example: Modifying the DCFIFO Contents at Runtime

This design example demonstrates the use of the Virtual JTAG megafunction and a command-line script

to dynamically modify the contents of a DCFIFO at runtime.

The Tcl API that ships with the Virtual JTAG megafunction makes it an ideal solution for developing

command-line scripts that can be used to either update data values or toggle control bits at run time. This

visibility into the FPGA can help expedite debug closure during the prototyping phase of the design, especially

when external equipment is not available to provide a stimulus.

This design example consists of a Quartus II project file that implements a DCFIFO and a command-line

script that is used to modify the contents of the FIFO at runtime.

The RTL consists of a single instantiation of the Virtual JTAG megafunction to communicate with the JTAG

circuitry. Both read and write ports of the DCFIFO are clocked at 50 MHz. A SignalTap II Logic Analyzer

instance taps the data output bus of the DCFIFO to read burst transactions from the DCFIFO. The following

sections discuss the RTL implementation and the runtime control of the DCFIFO using the Tcl API.

Write Logic

The RTL uses a single instance of the Virtual JTAG megafunction to decode both the instructions for the

write side and read side logic. The IR register is three bits wide, with the three instructions decoded in the

RTL, as shown in the table below.

Altera Corporation

Virtual JTAG Megafunction (sld_virtual_jtag)

37

Design Example: Modifying the DCFIFO Contents at Runtime

UG-SLDVRTL

2014.03.19