Clocked video input format detection, Clocked video input format detection -2 – Altera Video and Image Processing Suite User Manual

Page 61

Output IP cores still accept data on the Avalon-ST Video interface for as long as there is space in the input

FIFO.

The sequence for starting the output of the IP core:

1. Write a 1 to

Control

register bit 0.

2. Read

Status

register bit 0. When this bit is 1, the IP core produces data or video. This occurs on the

next start of frame or field boundary.

Note: For CVI IP cores, the frame or field matches the Field order parameter settings.

The sequence for stopping the output of the IP core:

1. Write a 0 to

Control

register bit 0.

2. Read

Status

register bit 0. When this bit is 0, the IP core has stopped data output. This occurs on the

next start of frame or field boundary

Note: For CVI IP cores, the frame or field matches the Field order parameter settings.

The starting and stopping of the IP core is synchronized to a frame or field boundary.

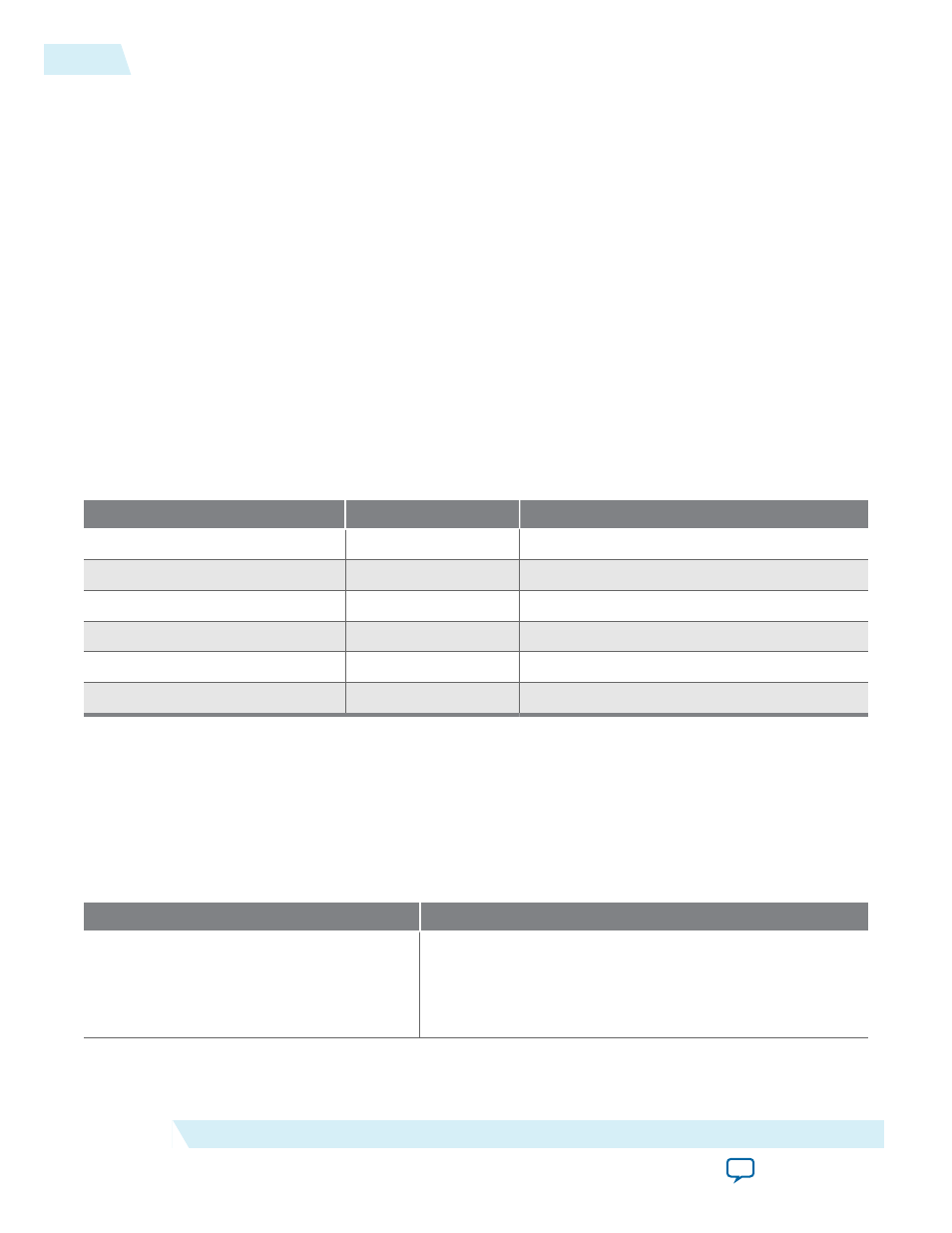

Table 4-2: Synchronization Settings for Clocked Video Input IP Cores

The table below lists the output of the CVI IP cores with the different Field order settings.

Video Format

Field Order

Output

Interlaced

F1 first

Start, F1, F0, ..., F1, F0, Stop

Interlaced

F0 first

Start, F0, F1, ..., F0, F1, Stop

Interlaced

Any field first

Start, F0 or F1, ... F0 or F1, Stop

Progressive

F1 first

No output

Progressive

F0 first

Start, F0, F0, ..., F0, F0, Stop

Progressive

Any field first

Start, F0, F0, ..., F0, F0, Stop

Clocked Video Input Format Detection

The CVI IP cores detect the format of the incoming clocked video and use it to create the Avalon-ST

Video control packet. The cores also provide this information in a set of registers.

Table 4-3: Format Detection

The CVI IP cores can detect different aspects of the incoming video stream.

Format

Description

Picture width (in samples)

• The IP core counts the total number of samples per line,

and the number of samples in the active picture period.

• One full line of video is required before the IP core can

determine the width.

4-2

Clocked Video Input Format Detection

UG-VIPSUITE

2015.05.04

Altera Corporation

Clocked Video Interface IP Cores