Additional information, Document revision history, How to contact altera – Altera Cyclone IV GX FPGA Development Board User Manual

Page 59

May 2013

Altera Corporation

Cyclone IV GX FPGA Development Board

Reference Manual

Additional Information

This chapter provides additional information about the document and Altera.

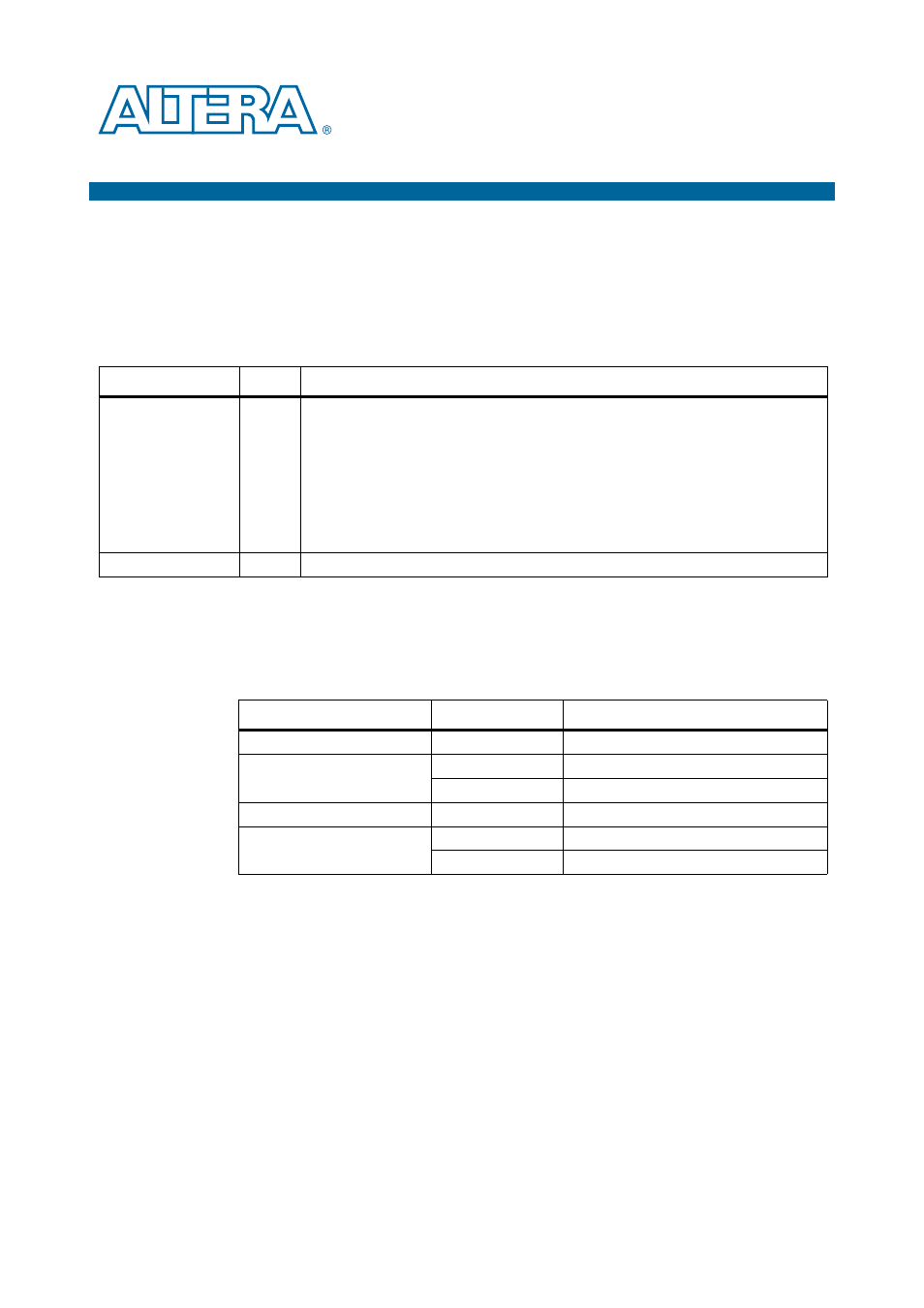

Document Revision History

The following table shows the revision history for this document.

How to Contact Altera

To locate the most up-to-date information about Altera products, refer to the

following table.

Date

Version

Changes

May 2013

1.1

■

Updated

—The I/O standard for user push buttons is 1.8-V.

■

Updated the note in

—All signals are translated from 1.8-V to 2.5-V using a

dual/quad low-voltage level translators except for LCD_DATA4.

■

Updated

—The I/O standard for PCI Express transmit and receive bus is

1.5-V PCML.

■

Updated

—HSMA pin J1.44 connects to FPGA pin AD27.

■

Updated the document template.

December 2010

1.0

Initial release.

Contact

Contact Method

Address

Technical support

Website

Technical training

Website

Product literature

Website

Nontechnical support (general)

(software licensing)

Note to Table:

(1) You can also contact your local Altera sales office or sales representative.