Measurement Computing CIO-INT-32 User Manual

Page 8

Table 2. Available IRQs

Note: IRQ8-15 are AT only

LPT

IRQ7

UNASSIGNED

IRQ15

FLOPPY DISK

IRQ6

HARD DISK

IRQ14

HARD DISK (AT)

LPT (AT)

IRQ5

80287 NUMERIC CO-P

IRQ13

COM OR SDLC

IRQ4

UNASSIGNED

IRQ12

COM OR SDLC

IRQ3

UNASSIGNED

IRQ11

RESERVED (XT)

INT 8-15 (AT)

IRQ2

UNASSIGNED

IRQ10

KEYBOARD

IRQ1

RE-DIRECTED TO IRQ2 (AT)

IRQ9

TIMER

IRQ0

REAL TIME CLOCK (AT)

IRQ8

PARITY

NMI

DESCRIPTION

NAME

DESCRIPTION

NAME

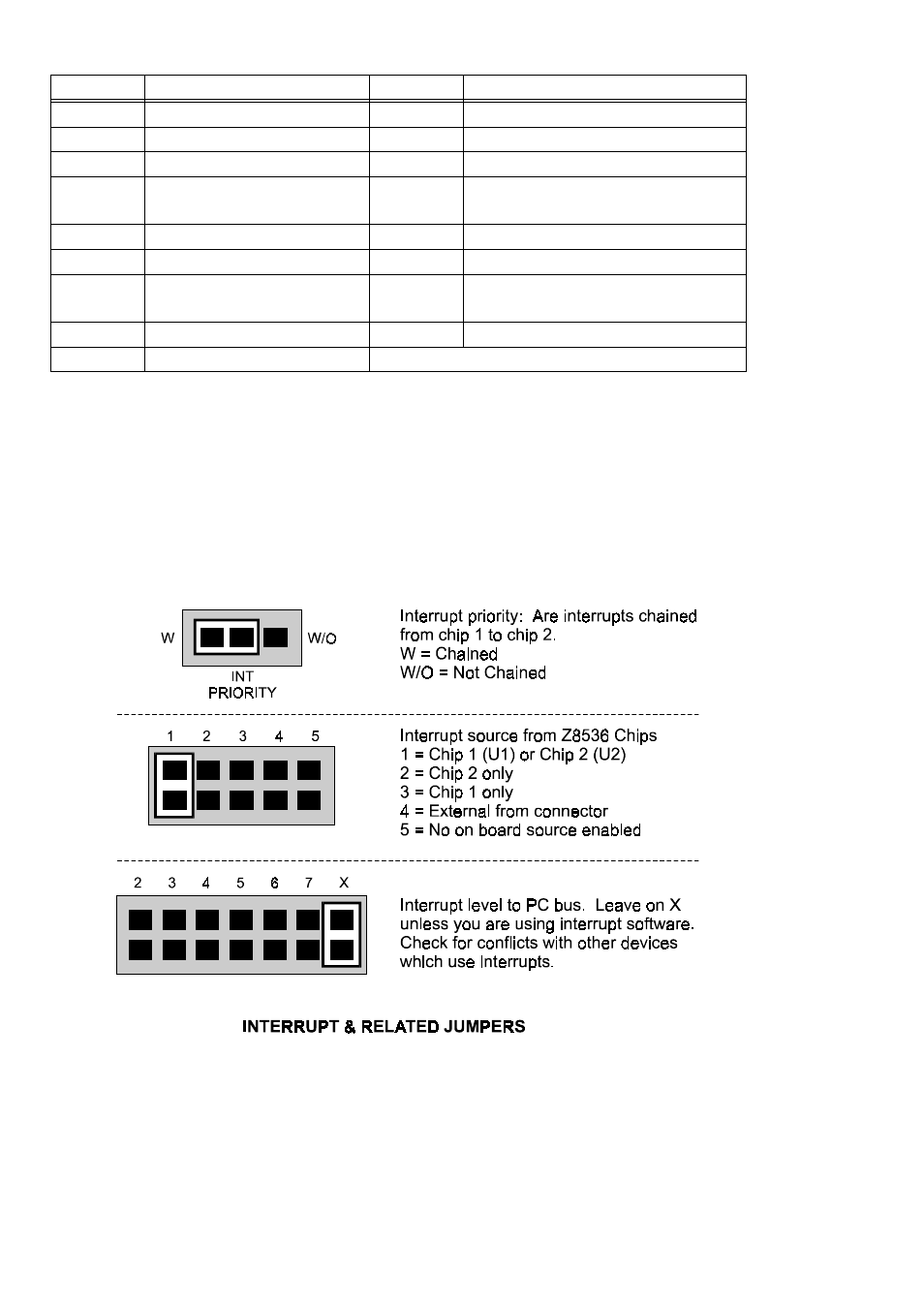

The CIO-INT32 may assert interrupts either:

1. From an external source brought to the connector.

2. Individually from each Z8536 for 16 external interrupt lines per chip

3. Chained as a set of 32 interrupt lines.

Choose a chained or unchained scheme by selecting chained (W) or not chained

(W/O) at the INT PRIORITY jumper.

Choose the source of the interrupt to be routed to the PC bus using the INT SRC

jumper. If the Z8536s are chained, you must choose 1 (Chip 1 or Chip 2).

4