Resetting the altchip_id ip core, Document revision history – Altera Unique Chip ID User Manual

Page 11

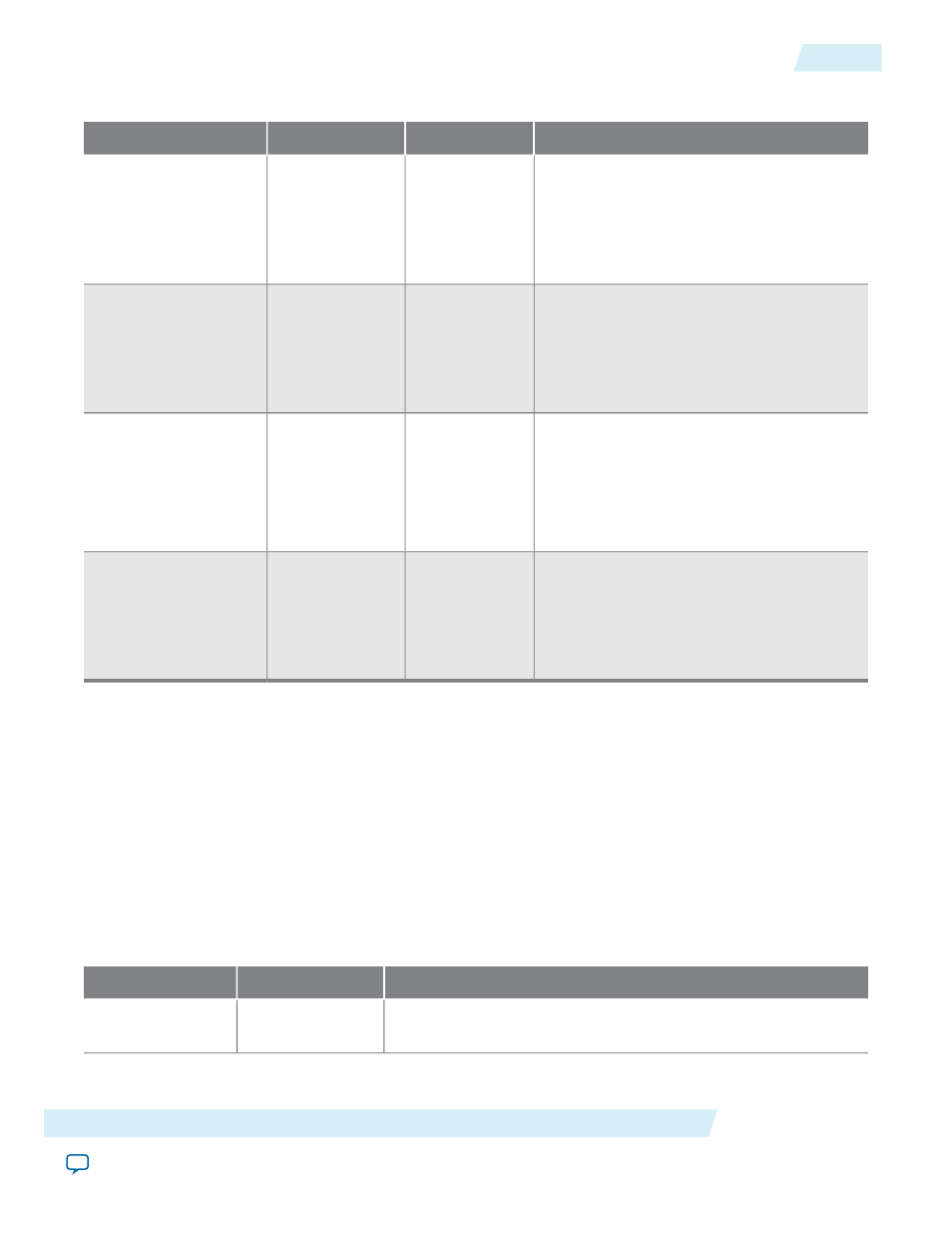

Table 2: ALTCHIP_ID Ports

Description

Size (in Bit)

I/O

Port

Feeds clock signal to the chip ID block. The

maximum supported frequency is 100 MHz.

When you provide a clock signal, the IP core

reads the value of the unique chip ID and

sends the value to the

chip_id

output port.

1

Input

clkin

Resets the IP core when you assert high to

the reset signal for at least one clock cycle.

The

chip_id [63:0]

output port holds the

value of the unique chip ID until you

reconfigure the device or reset the IP core.

1

Input

reset

Indicates that the unique chip ID is ready for

retrieval. If the signal is low, the IP core is in

initial state or in progress to load data from

a fuse ID. After the IP core asserts the signal,

the data is ready for retrieval at the

chip_

id[63..0]

output port.

1

Output

data_valid

Indicates the unique chip ID according to its

respective fuse ID location. The data is only

valid after the IP core asserts the

data_valid

signal.

The value at power-up resets to

0

.

64

Output

chip_id

Resetting the ALTCHIP_ID IP Core

To reset the ALTCHIP_ID IP core, you must assert high to the reset signal for at least one clock cycle. After

you deassert the reset signal, the ALTCHIP_ID IP core rereads the unique chip ID from the fuse ID block.

The ALTCHIP_ID IP core asserts the

data_valid

signal after completing the operation.

Document Revision History

The following table lists the revision history for this document.

Table 3: Date Version Changes

Changes

Version

Date

• Updated document title to reflect new name of "Altera Unique

Chip ID" IP core.

2014.09.02

September, 2014

Altera Corporation

Altera Unique Chip ID IP Core User Guide

11

Resetting the ALTCHIP_ID IP Core

ug-altchipid

2014.09.02