Altera DDR SDRAM Controller User Manual

Page 80

A–2

Parameters

DDR and DDR2 SDRAM Controller Compiler User Guide

© March 2009

Altera Corporation

shows the postamble options (DQS mode only).

f

For more information on the resynchronization options, refer to

).

Dedicated clock phase

0 to 359

This parameter is available only when you select Dedicated

for the Resynchronization clock setting. You can enter the

phase of the dedicated resynchronization clock for timing

analysis. IP Toolbench uses this value to set up the PLL

phase shift.

Fed-back clock phase

0 to 359

Allows you to enter the phase of the fed-back clock that is

used for timing analysis. IP Toolbench uses this value to set

up the PLL phase shift.

Insert intermediate

resynchronization registers

On or off

When turned on, an extra pipeline register, clocked on the

negative edge of system clock, is inserted in the read path

after the resynchronization registers. Turn on when the

resynchronization clock is too close to the system clock for

reliable transfer between them. Refer to

Resynchronization Registers” on page A–10

.

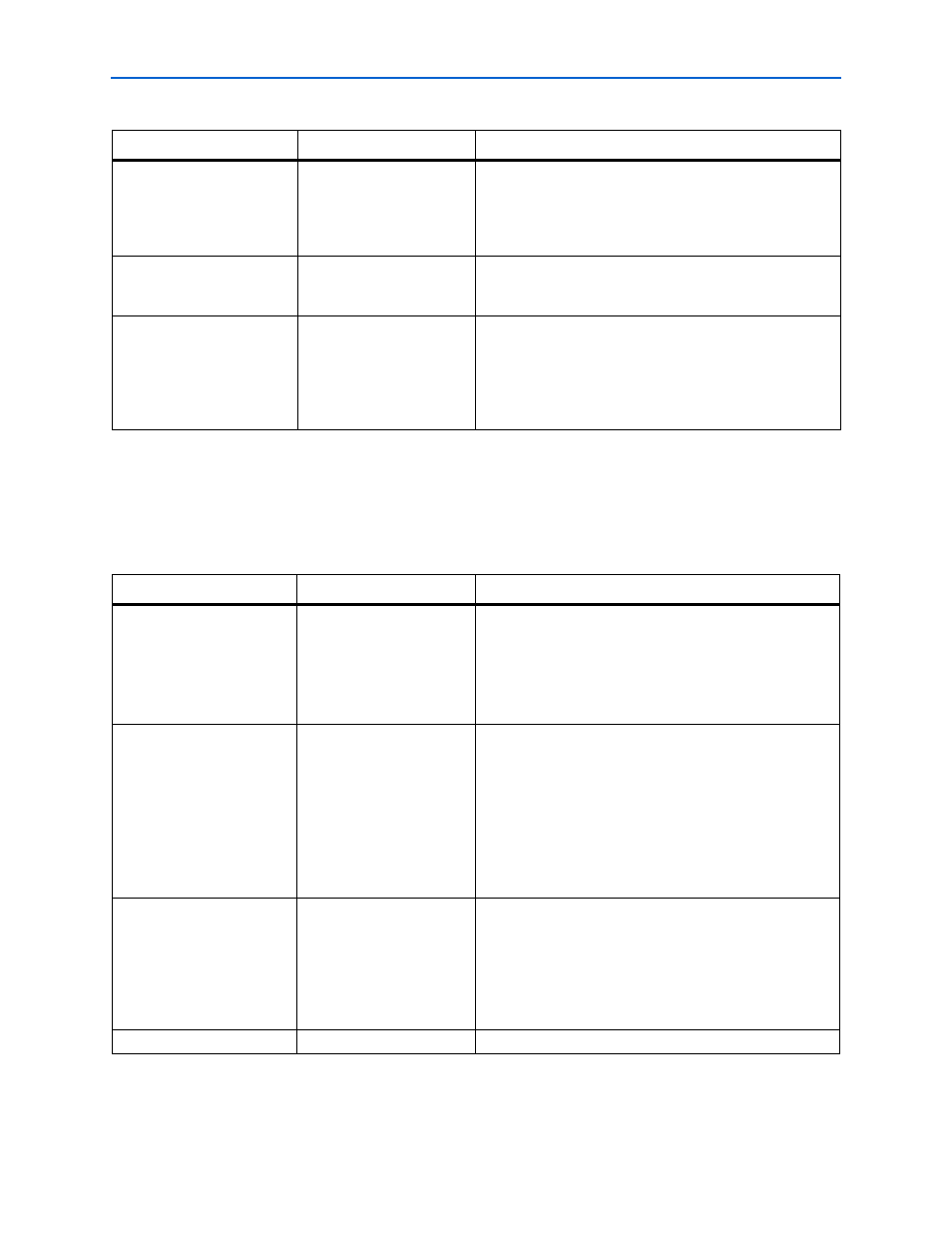

Table A–1. Resynchronization Options (Part 2 of 2)

Parameter

Range

Description

Table A–2. Postamble Options (Part 1 of 2)

Parameter

Range

Description

Manual postamble control

On or off

Turn on to specify the details of the postamble logic clock

and to set the postamble clock phase manually. Otherwise,

the details are calculated automatically based on system

timing.

This option is only available when you turn on Enable DQS

Mode in the controller settings tab.

Enable DQS postamble logic

On or off

When turned on, the postamble logic is used. If the

postamble logic is not used, there is a possibility of data loss

in the last transfer of each read burst.

Turn on to use the postamble logic. Turn off to remove the

postamble logic from the design (refer to

). When you turn off

the postamble logic you may see data loss in the last transfer

of each burst read. If you turn off this option, you must

ensure the read capture occurs correctly.

Insert intermediate

postamble registers

On or off

When turned on, the doing_rd_delayed signal is

generated using the positive edge of the system clock and

when turned off, doing_rd_delayed is generated using

the negative edge of the system clock. Turn on when the

negative edge of the system clock is too close to the positive

edge of the postamble clock. Refer to

Postamble Registers” on page A–12

Postamble cycle

0 to 6

The number of cycles of delay to allow for round-trip delay.