Altera Dynamic Calibrated On-Chip Termination User Manual

Page 6

2–2

Chapter 2: Parameter Settings

MegaWizard Parameter Settings

Dynamic Calibrated On-Chip Termination (ALTOCT) Megafunction

February 2012

Altera Corporation

User Guide

3

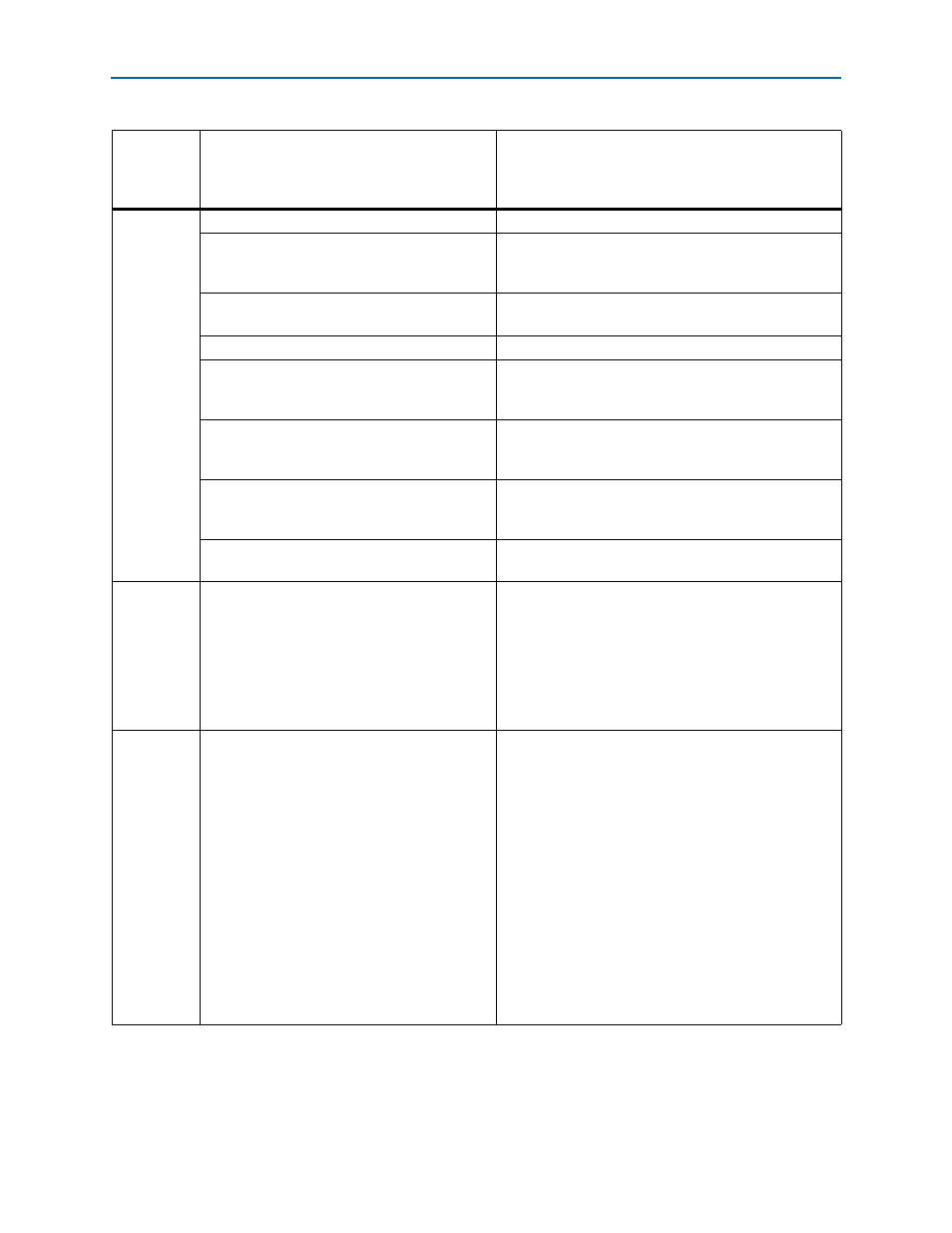

Currently selected device family

Specifies the device family you chose on page 2a.

Match project/default

Turn on this option to ensure that the device selected

matches the device family that is chosen in the previous

page.

Calibrate OCT on power-up

Turn on this option if you want to calibrate OCT on

power-up.

How many OCT blocks should be used?

Specify the number of OCT blocks for your design.

Enable parallel termination

Turn on this option if you want to enable parallel

termination instead of series termination. Observe the

changes in resource usage when this option is enabled.

Create ‘calibration_wait’ input port to prevent

calibration

The

calibration_wait

input port can be used to halt

calibration operation. This option is for advanced users

only. Typical users should not enable this option.

Create ‘clken’ input port

The

clken

input port is used as the clock enable signal.

This option is for advanced users only. Typical users

should not enable this option.

Enable independent calibration/shift

Turn on this option to enable independent

calibration/shift.

4

Generate netlist

Turn on this option if you want to generate a netlist for

your third-party EDA synthesis tool to estimate the timing

and resource usage of the megafunction. If you turn on

this option, a netlist file (_syn.v) is generated. This file is

a representation of the customized logic used in the

Quartus

®

II software and provides the connectivity of the

architectural elements in the megafunction but may not

represent true functionality.

5

Summary Page

Specify the types of files to be generated. The Variation

file (<function name>.v) contains wrapper code in the

language you specified on page 2a and is automatically

generated. Choose from the following types of files:

■

AHDL Include file (<function name>.inc)

■

VHDL component declaration file

(<function name>.cmp)

■

Quartus II symbol file (<function name>.bsf)

■

Instantiation template file (<function name>_inst.v)

■

Verilog HDL black box file (<function name>_bb.v)

For more information about the wizard-generated files,

refer to the Quartus II Help or to the

chapter in volume 1 of the Quartus II

Handbook.

Table 2–1. ALTOCT MegaWizard Plug-In Manager Page Options and Description (Part 2 of 2)

MegaWizard

Plug-in

Manager

Page

Configuration Setting

Description