Zilog Z16C35 User Manual

Page 275

Application Note

Boost Your System Performance Using The Zilog ESCC

™

13-8

AUTOMATIC OPENING FLAG TRANSMISSION

When Auto Tx Flag (WR7', D0) is enabled, the ESCC

automatically transmits a SDLC opening flag before

transmitting data. This removes:

1.

Requirements to reset the mark idle bit (WR10 D3)

before writing data to the transmitter, or;

2.

Waiting for eight bit times to load the opening flag.

TxD Forced High In SDLC With NRZI Encod-

ing When Marking Idle After End Of Frame

When the ESCC is programmed for SDLC mode with NRZI

encoding and mark idle (WR10 D6=0,D5=1,D3=1), TxD is

automatically forced high when the transmitter goes to the

mark idle state at EOF or when Abort is detected. This

feature is used in combination with the automatic SDLC

opening flag transmission to format the data packets

between successive frames properly without any

requirement in software intervention.

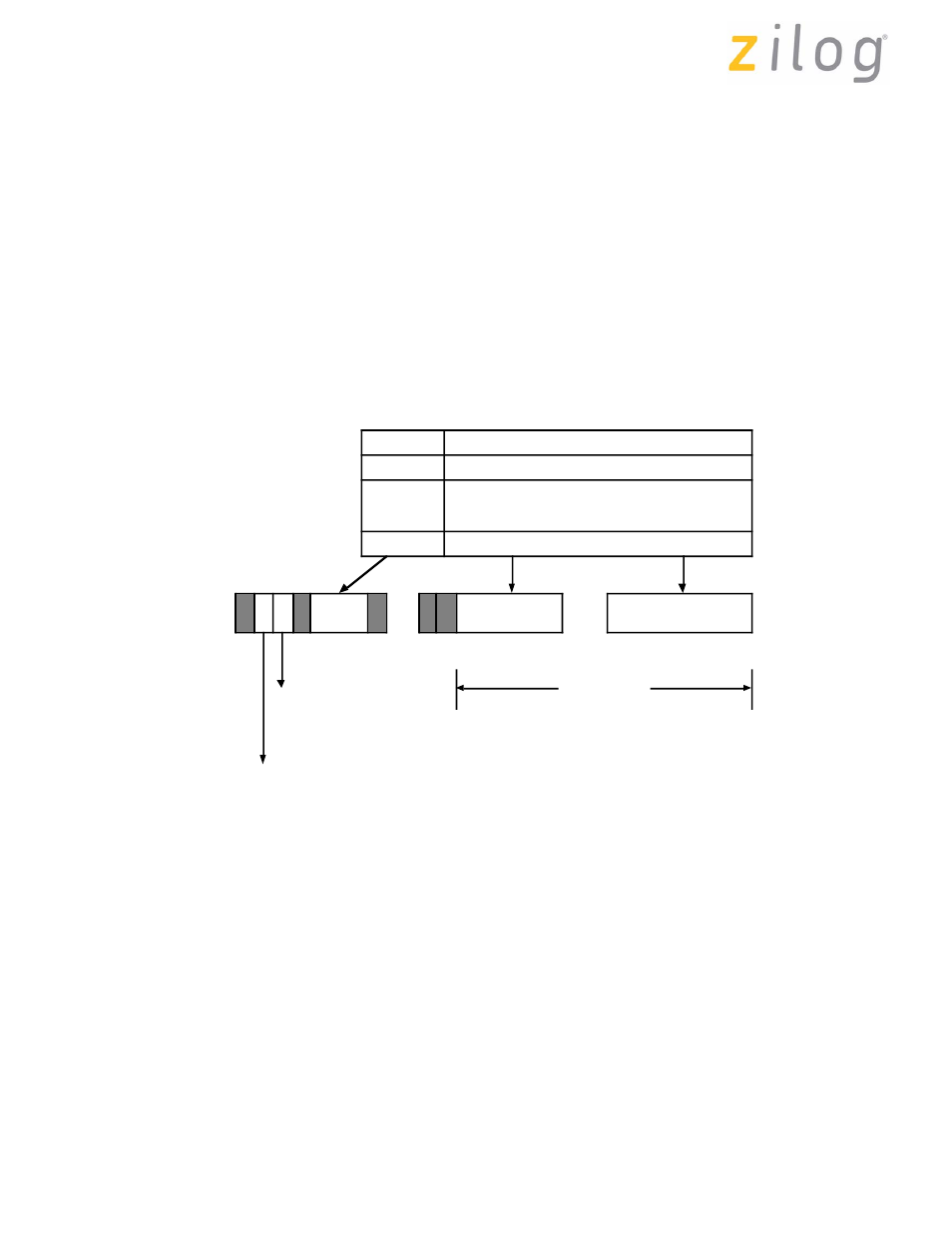

Status FIFO Enhancement

ESCC SDLC Frame Status FIFO implementation has

been improved to maximize ESCC ability to interface with

a DMA-driven system (Technical Manual, 4.4.3). The

Status FIFO and its relationship with RR1, RR6 and RR7

is shown in Figure 8.

Other special conditions (e.g., Overrun) generates special

receive conditions and lock the Receiver FIFO (Figures 9

and 10).

Figure 8. Status FIFO

Loaded If

Status FIFO

Is Enabled

Status

FIFO

RR7

RR6

Byte Count

Residue

Code

RX

Overrun

Error

CRC/Framing

Error

RR1

Page 269 of 316

UM011002-0808