Fc100 - floating point fast fourier transform, Clock enable – Sundance FC100 v.2.3 User Manual

Page 5

FC100 - Floating Point Fast Fourier Transform

v2.3

Fast Fourier Transform product manual

October 2005

www.sundance.com

- 5 -

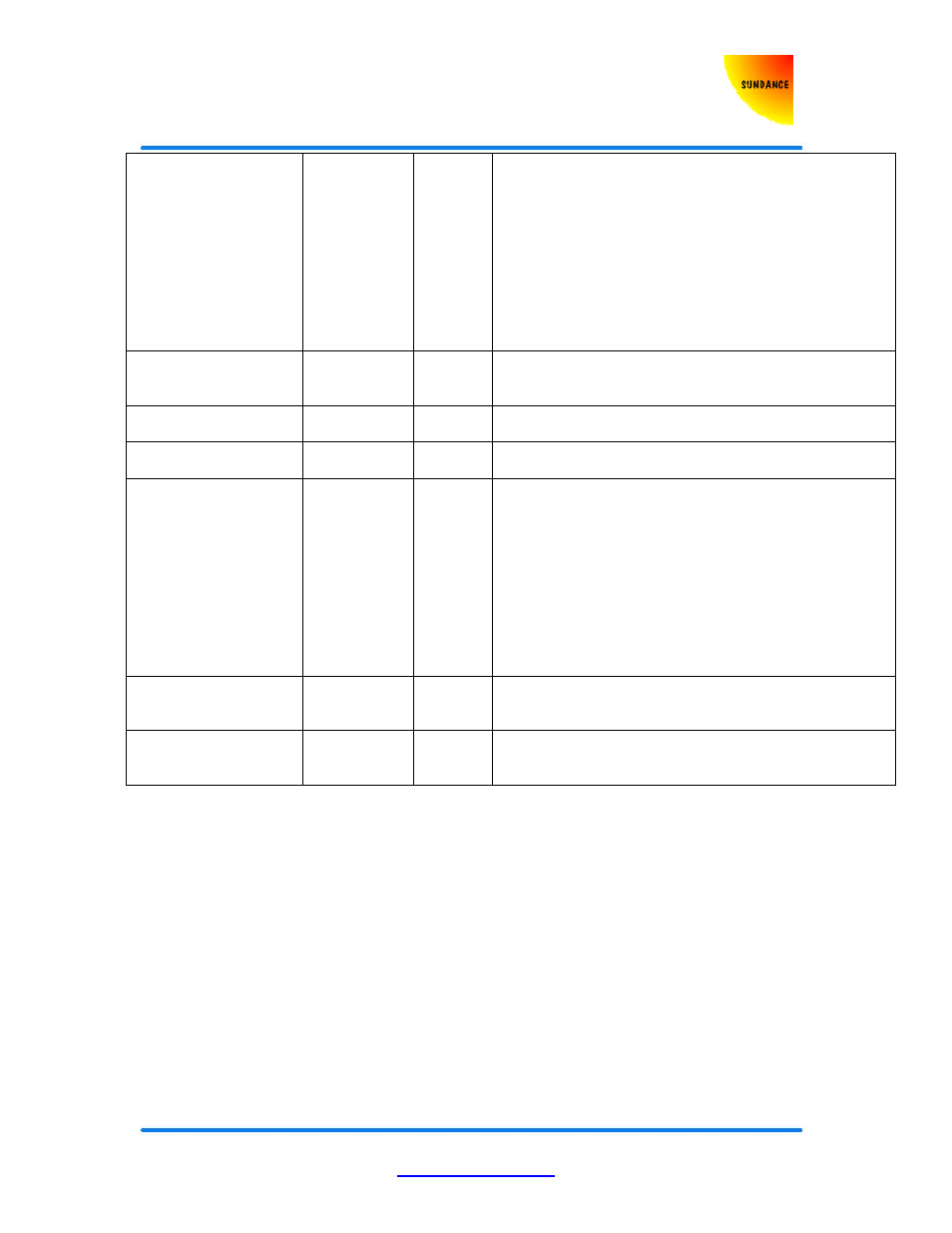

din

2.Mbw+2.Ebw

or 64 for

IEEE-754

Input

Data input. This bus should be connected to the input data

bank currently used for processing. The data decomposition is

as follows for 2’s complement formats:

Real mantissa: bits Mbw-1 down to 0

Imag mantissa: bits 2.Mbw-1 down to Mbw

Real exponent: bits 2.Mbw+ Ebw-1 down to 2.Mbw

Imag exponent: bits 2.Mbw+ 2.Ebw-1 down to 2.Mbw+ Ebw

IEEE-754:

Real : bits 31 down to 0

Imag : bits 63 down to 32

tw_din_valid

1

Input Twiddle factors, data input valid. This signal should be

asserted high when the data input (din) and twiddle factors

(tw) are valid on the bus.

dout_addr

Abw

Output

Data output and results address. This bus gives the address in

the memory where the output data (dout) must be written to.

dout_bank

1

Output

Data output memory bank. This signal indicates which data

memory bank is used as the output bank.

dout

2.Mbw+2.Ebw

or 64 for

IEEE-754

Output

Data output. This bus should be connected to the output data

bank currently used for processing. The data decomposition is

as follows for 2’s complement formats:

Real mantissa: bits Mbw-1 down to 0

Imag mantissa: bits 2.Mbw-1 down to Mbw

Real exponent: bits 2.Mbw+ Ebw-1 down to 2.Mbw

Imag exponent: bits 2.Mbw+ 2.Ebw-1 down to 2.Mbw+ Ebw

IEEE-754:

Real : bits 31 down to 0

Imag : bits 63 down to 32

dout_valid

1

Output

Data out valid strobe. This signal indicates that the data on

the dout bus are valid and can be written to a memory bank

for further processing.

result_valid

1

Output

Result valid strobe. This signal indicates that the data on the

dout bus are the final results of the transform and must be

written to the results memory bank.

Table 2 : Ports definition

Clock enable

The clock enable signal should be handled with great care. Due to the internal complexity

of the FFT core, the use of the clock enable signal is subject to the following rules in

order to ensure proper operation of the core:

When a new FFT is started (start pulse), the cke signal must remain high at least

till the first sample is written to the core.

The cke signal can be driven low only during the data loading phase (first pass

through the core) and during the results offloading phase (last pass though the

core). During intermediate passes, the cke signal must remain high.

When forced low, the cke signal must remain low for at least 4 consecutive

clock cycles.