Adc control – Sundance SMT356 User Manual

Page 7

Version 2.1

Page 7 of 26

SMT356356 User Manual

ADC Control

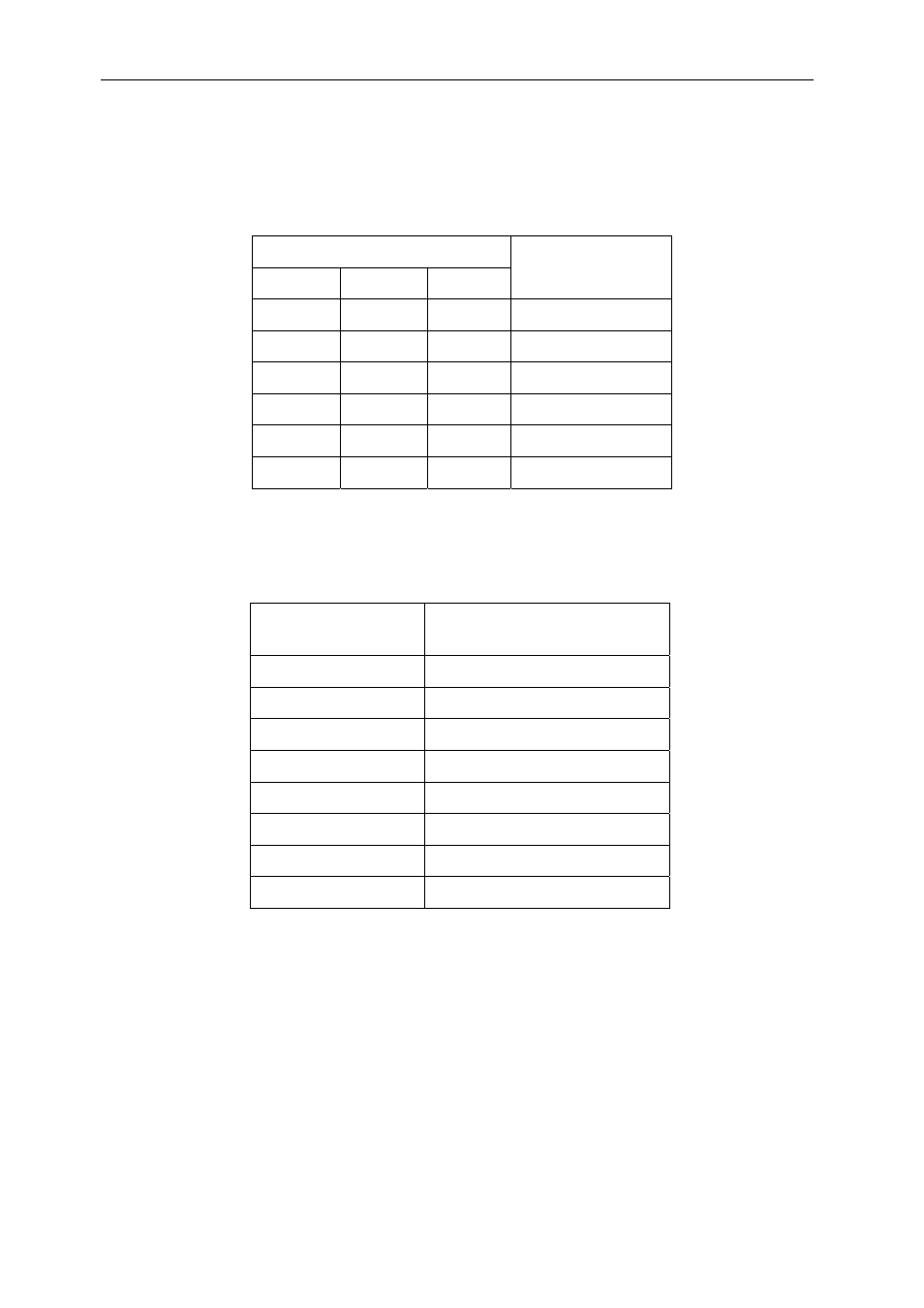

All of the ADCs are controlled via one of the six available ‘C40 style comm ports. The

desired comm port must be selected using the jumper bank JP1.

JP1 – positions 5-7

Comm Port

7 6 5

ON ON ON

0

ON ON OFF

1

ON OFF ON

2

ON OFF OFF

3

OFF ON ON

4

OFF ON OFF

5

This interface contains a single control register. This controls the clock divider, clock

enable, ADC enable and the state of the four LEDs. This register is described here,

Control Register

Data Bits

Function

D7-0 Clock

Divider

D15-8 ADC

Enable

D19-16 LED4-1

control

D20 Clock

enable

D21

Clock enable mode

D22 SDB

mode

D23 Reset

FIFO

D31-24 Sample

count

Bit D20 of this register controls the ADC clock enable via software. A ‘1’ enables the

ADC, or generates a rising edge trigger (depending on clock enable mode). The

power-on state of this bit is ‘0’.

Bit D21 controls the clock enable mode. A ‘0’ selects latched counter mode, a ‘1’

selects direct control. The power-on state of this bit is ‘0’.