Simulating the design, Testbench, Simulating the design –8 – Altera Serial Digital Interface (SDI) MegaCore Function User Manual

Page 22: Testbench –8

2–8

Chapter 2: Getting Started

Simulating the Design

Serial Digital Interface (SDI) MegaCore Function

February 2013

Altera Corporation

User Guide

Simulating the Design

This section describes the following simulation techniques:

■

Simulate with IP Functional Simulation Models

■

Simulating with the ModelSim Simulator

■

Simulating in Third-Party Simulation Tools Using NativeLink

Testbench

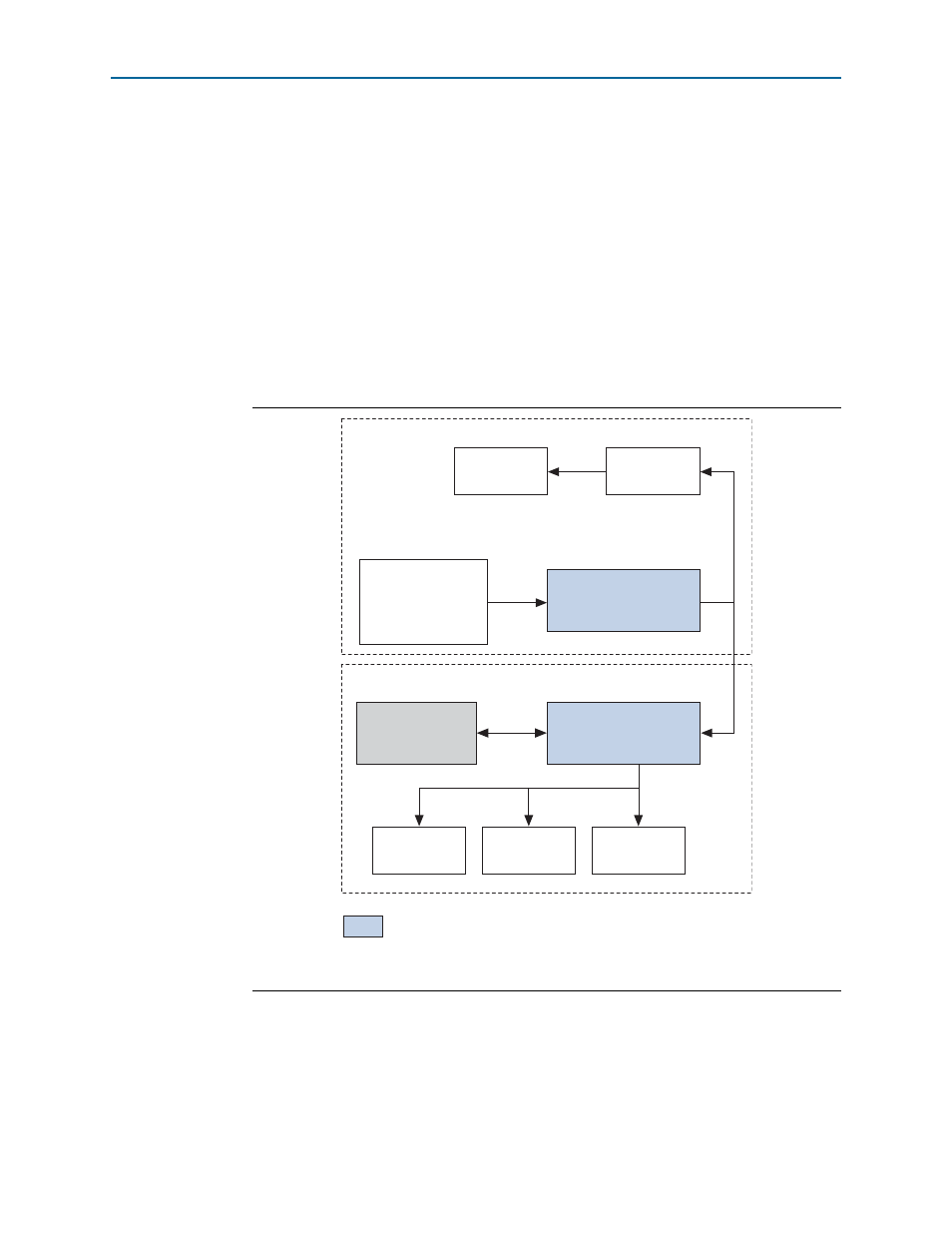

In general, all testbenches are constructed in such a way that the serial transmit data is

looped back to receiver.

shows how the serial transmit data is looped back

to the receiver in the testbench.

Figure 2–2. General Simulation Testbench

Note to

:

(1) For dual or triple standard only.

ALTGXB

RECONFIG (1)

- SD 270 Mbps

- HD 1.485 Gbps

- 3G 2.97 Gbps

SDI Pattern Generator

SDI IP CORE - Receiver

SDI IP CORE - Transmitter

SDI TRANSMIT TEST

DUT

SDI RECEIVE TEST

Transmitter Data

Descrambler

Transmitter TRS

Counter

Receiver TRS

Checker

Receiver Lock

Checker

Receiver Line

Checker