Altera Serial Digital Interface (SDI) MegaCore Function User Manual

Page 33

Chapter 3: Functional Description

3–3

Block Description

February 2013

Altera Corporation

Serial Digital Interface (SDI) MegaCore Function

User Guide

■

Internal switching between two reference clock signals in the transmitter block.

This feature is optional and only available for Arria II GZ, Stratix IV GX , and

HardCopy IV devices.

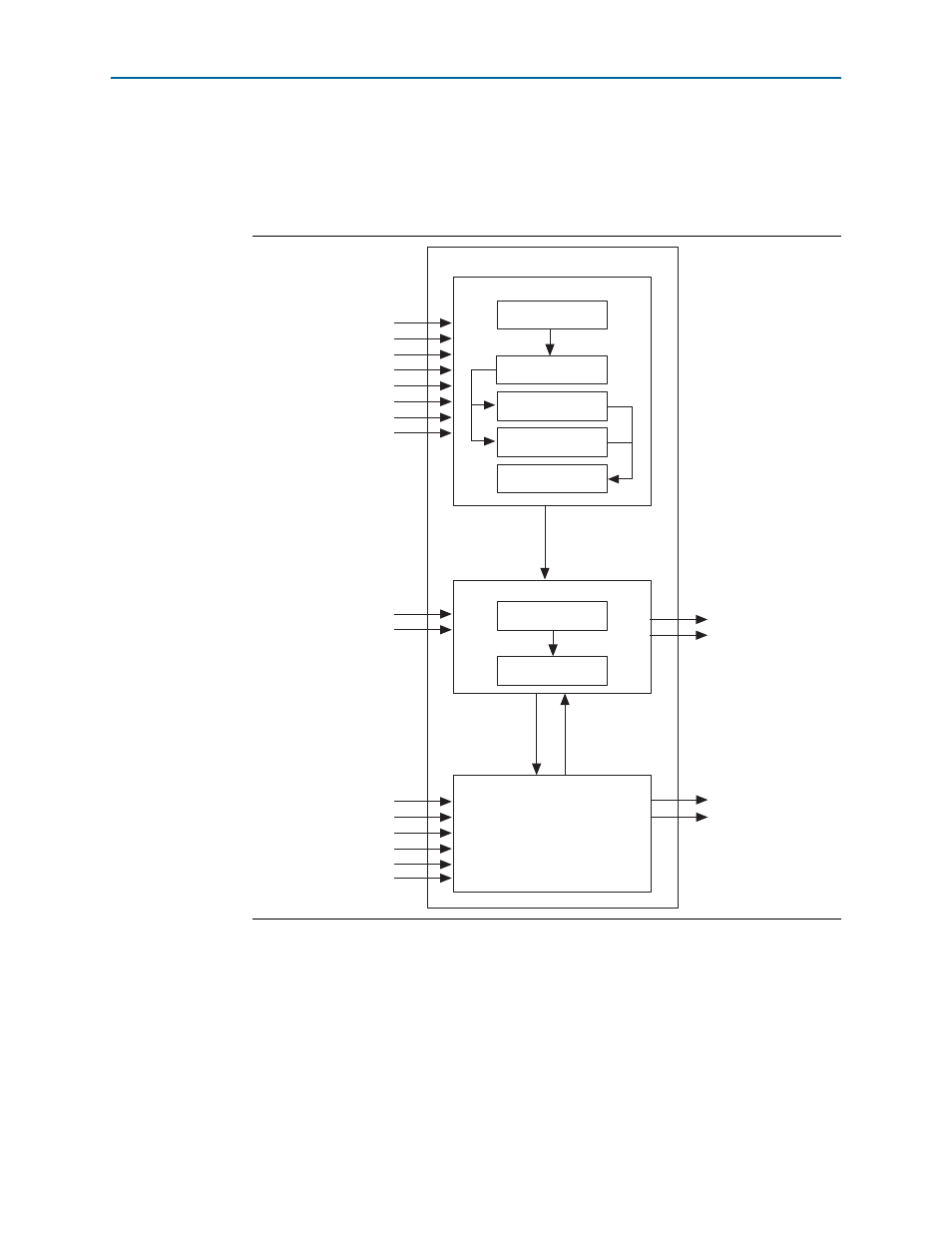

shows the top-level block diagram for the SDI transmitter.

For HD-SDI, the transmitter accepts 20-bit parallel video data; for SD-SDI, 10-bit

parallel data. For txdata bus definition, refer to

Figure 3–2. SDI Transmitter Block Diagram

TRS Match

SDI TRANSMITTER

Protocol Block

Transceiver Interface Block

Transceiver Block

LN Insert

CRC (c)

CRC (y)

Scrambler

FIFO

GXB RX Sample

rst_tx

tx_pclk

reset

tx_serial_refclk

tx_serial_refclk1 (optional)

gxb4_cal_clk

sdi_reconfig_togxb[3:0]

sdi_gxb_powerdown

rst_tx

tx_pclk

txdata[19:0]

tx_std[1:0]

tx_trs

tx_ln[21:0]

enable_ln

enable_crc

tx_status

gxb_tx_clkout

sdi_tx (serial data)

sdi_reconfig_fromgxb[16

tx_data[19:0]

tx_cloc

kout

tx_datain[19:0]