Clock summary – Altera Stratix V Avalon-MM Interface for PCIe Solutions User Manual

Page 112

Advertising

Clock Summary

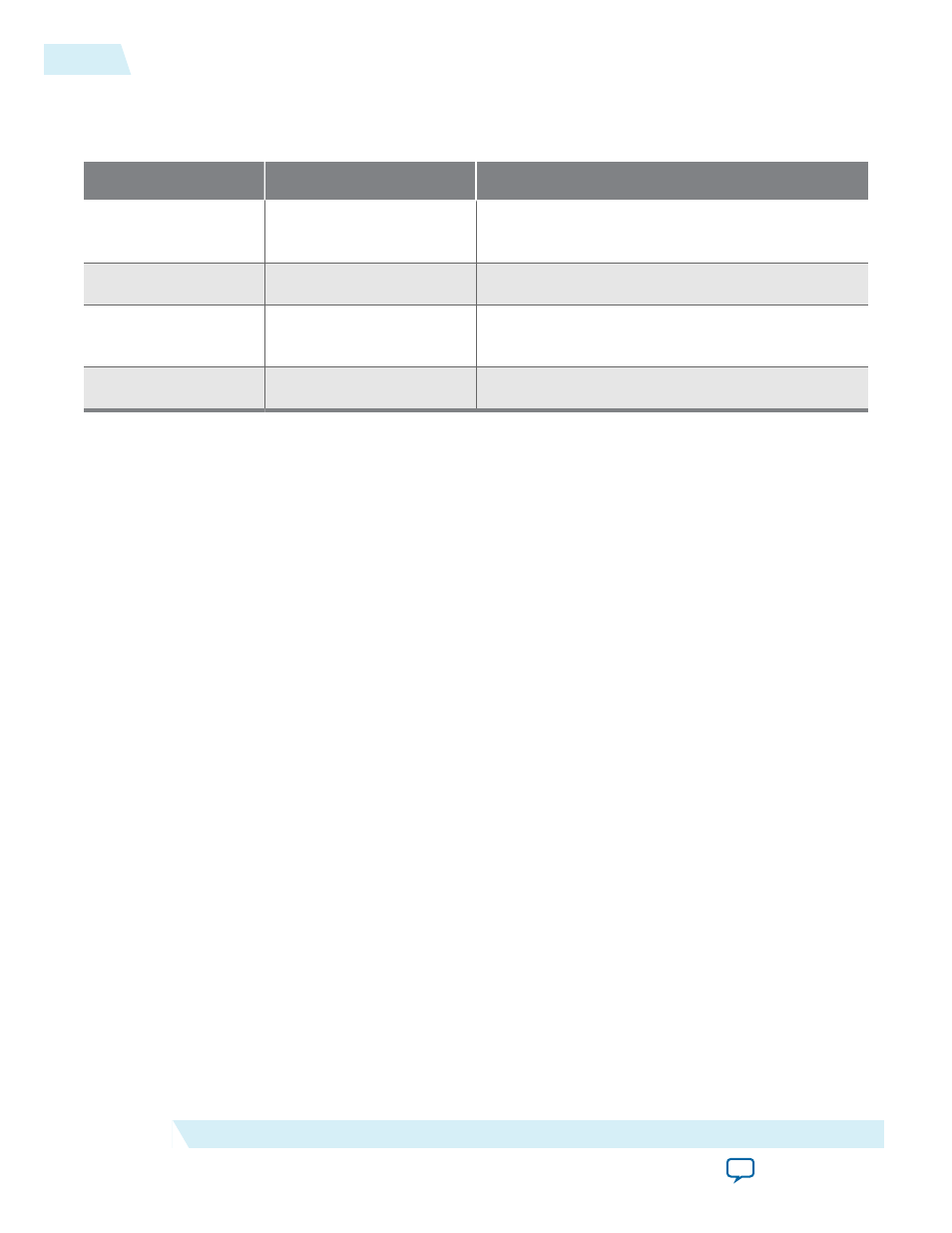

Table 6-4: Clock Summary

Name

Frequency

Clock Domain

coreclkout_hip

62.5, 125 or 250 MHz

Avalon-ST interface between the Transaction and

Application Layers.

pld_clk

62.5, 125, or 250 MHz

Application and Transaction Layers.

refclk

100 or 125 MHz

SERDES (transceiver). Dedicated free running input

clock to the SERDES block.

reconfig_xcvr_clk

100 –125 MHz

Transceiver Reconfiguration Controller.

6-8

Clock Summary

UG-01097_avmm

2014.12.15

Altera Corporation

Reset and Clocks

Advertising

This manual is related to the following products: