Serial structures –7 multibit serial structure –7, Serial structures, Multibit serial structure – Altera FIR Compiler User Manual

Page 49

Chapter 4: Functional Description

4–7

FIR Compiler

© May 2011

Altera Corporation

Serial Structures

A serial structure trades off area for speed. The filter processes input data one bit at-a-

time per clock cycle. Therefore, serial structures require N clock cycles (where N is the

input data width) to calculate an output. In the Stratix IV, Stratix III, Stratix II, Stratix,

Cyclone III, Cyclone II, and Cyclone device families, using memory blocks for data

storage will result in a significant reduction in area.

shows the serial filter block diagram.

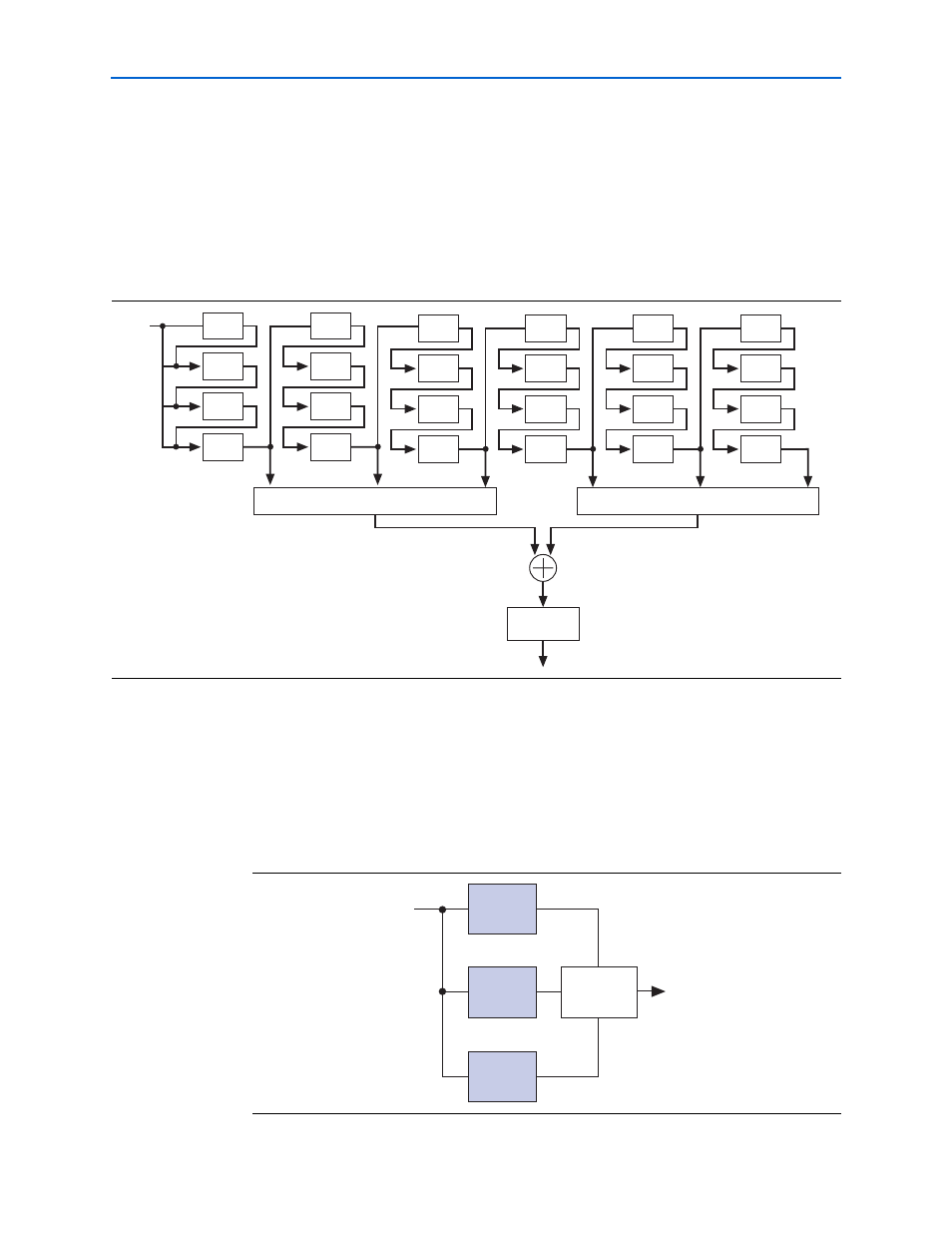

Multibit Serial Structure

A multibit serial structure combines several small serial FIR filters in parallel to

generate the FIR result. This structure provides greater throughput than a standard

serial structure while using less area than a fully parallel structure, allowing you to

trade off device area for speed.

shows the multibit serial structure.

Figure 4–4. Serial Filter Block Diagram

yout

Bit Array Multiplier

Bit Array Multiplier

xin

D Q

D Q

D Q

D Q

D Q

D Q

D Q

D Q

D Q

D Q

D Q

D Q

D Q

D Q

D Q

D Q

D Q

D Q

D Q

D Q

D Q

D Q

D Q

D Q

Serial

Accumulator

Figure 4–5. Multibit Serial Structure

Serial

FIR

Filter

Serial

FIR

Filter

Serial

FIR

Filter

Input

Data

Filtered

Data

FIR Compiler

Created Glue

Logic