Altera Arria V GX Starter Board User Manual

Page 29

Chapter 2: Board Components

2–21

Clock Circuitry

November 2013

Altera Corporation

Arria V GX Starter Board

Reference Manual

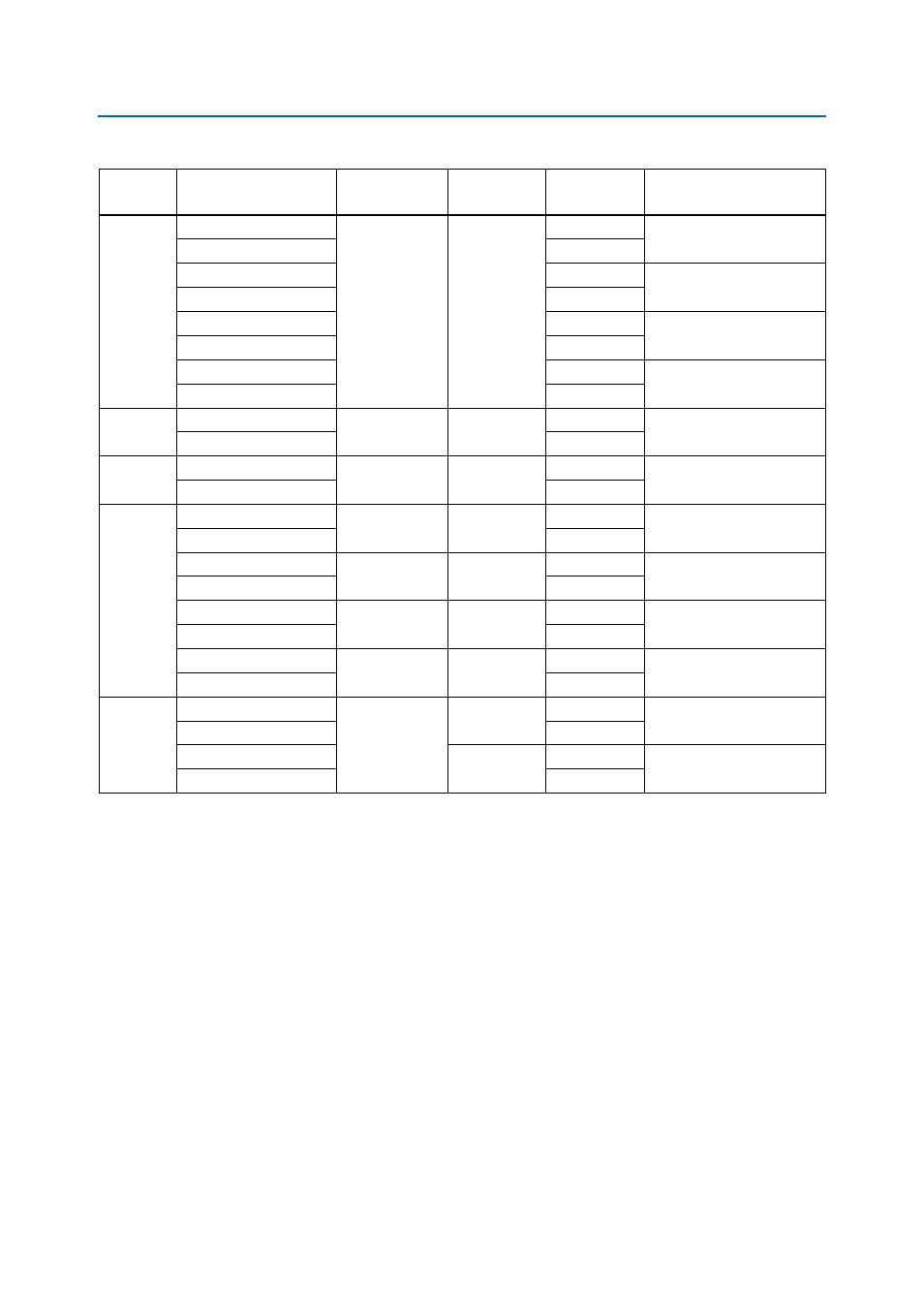

U5

REFCLK2_QL1_P

125.000 MHz

LVDS

(fanout buffer)

U26

Left transceiver bank

REFCLK2_QL1_N

U27

CLKINBOT_125_P

AP32

Bottom edge

CLKINBOT_125_N

AP31

CLKINTOP_125_P

A3

Top edge

CLKINTOP_125_N

B3

REFCLK2_QR1_P

U9

HSMC port A

REFCLK2_QR1_N

U8

X2

CLK_125_P

125.000 MHz

LVDS

AH17

10/100/1000 Ethernet

CLK_125_N

AG17

X1

CLK_148_P

148.500 MHz

LVDS

R26

HD-SDI video

CLK_148_N

R27

U4

Si5338A_CLK0_125_P

125.000 MHz

LVDS

(fanout buffer)

—

LVDS fanout buffer

Si5338A_CLK0_125_N

—

REFCLK1_QL0_P

409.600 MHz

LVDS

W26

SMA

REFCLK1_QL0_N

W27

REFCLK1_QR0_P

156.250 MHz

LVDS

W9

HSMC port A

REFCLK1_QR0_N

W8

Si5338A_CLK3_100_P

100.000 MHz

LVDS

(fanout buffer)

—

LVDS fanout buffer

Si5338A_CLK3_100_N

—

U3

CLKINTOP_100_P

100.000 MHz

LVDS

A19

Top edge—DDR3

CLKINTOP_100_N

A20

CLKINBOT_100_P

LVDS

AH18

Bottom edge

CLKINBOT_100_N

AG18

Table 2–14. On-Board Oscillators

Source

Schematic Signal Name

Frequency

I/O Standard

Arria V GX Pin

Number

Application