Maps and registers – Artesyn COMX-P4080 Installation and Use (August 2014) User Manual

Page 76

Maps and Registers

COMX-P4080 COM Express Module Installation and Use (6806800L20C)

76

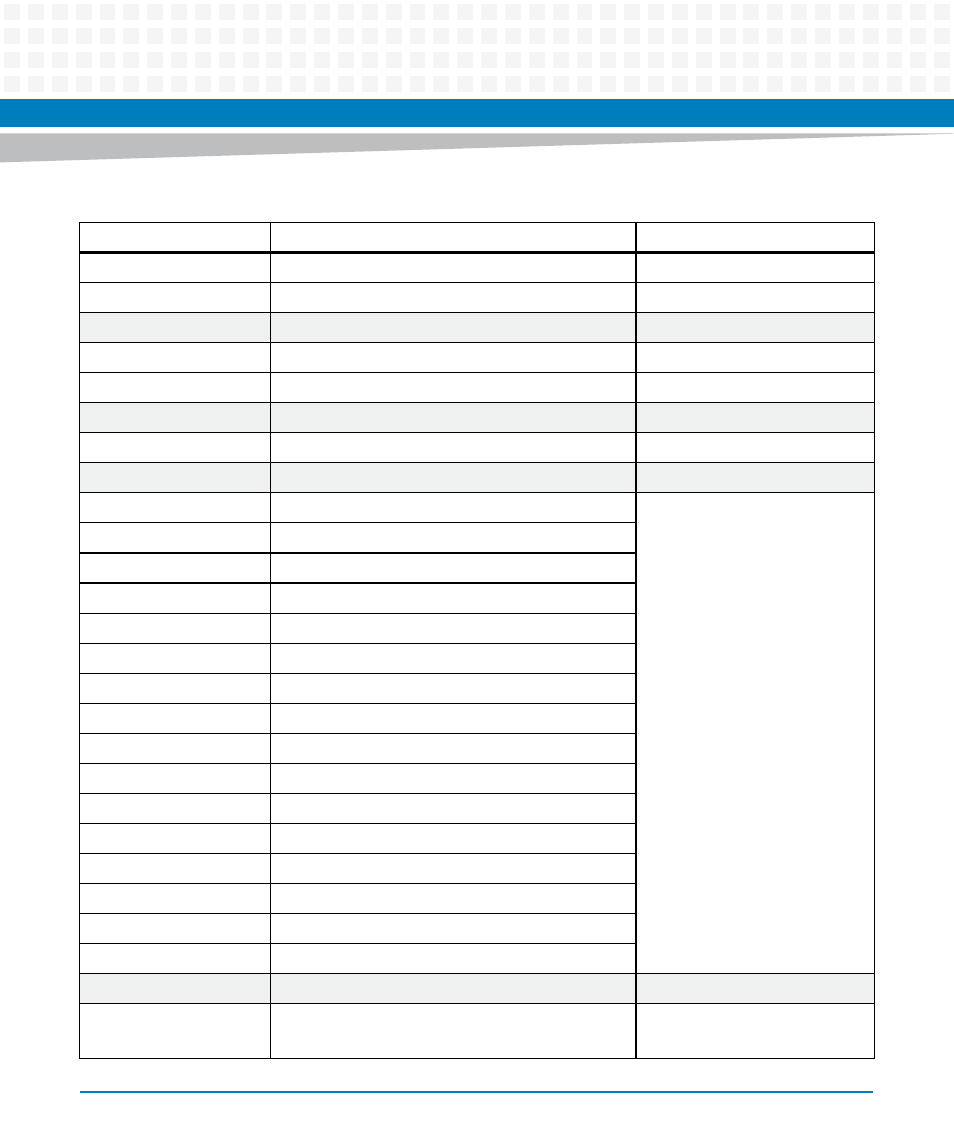

0x00_8000

DDR memory controller 1

-

0x00_9000

DDR memory controller 2

-

0x00_A000–0x00_FFFF

Reserved

-

0x01_0000

CoreNet platform cache 1 (CPC1)

-

0x01_1000

CoreNet platform cache 2 (CPC2)

-

0x01_2000–0x01_7FFF

Reserved

-

0x01_8000

CoreNet coherency fabric (CCF)

-

0x01_9000–0x01_FFFF

Reserved

-

0x02_0000

PAMU partition 1

The PAMU is partitioned into 16

identical instances. Not all are

necessarily backed with physical

hardware. However, all of them

must be programmed identically

or undefined behavior may

result.

0x02_1000

PAMU partition 2

0x02_2000

PAMU partition 3

0x02_3000

PAMU partition 4

0x02_4000

PAMU partition 5

0x02_5000

PAMU partition 6

0x02_6000

PAMU partition 7

0x02_7000

PAMU partition 8

0x02_8000

PAMU partition 9

0x02_9000

PAMU partition 10

0x02_A000

PAMU partition 11

0x02_B000

PAMU partition 12

0x02_C000

PAMU partition 13

0x02_D000

PAMU partition 14

0x02_E000

PAMU partition 15

0x02_F000

PAMU partition 16

0x03_0000–0x03_FFFF

Reserved

-

0x04_0000

PIC—Global registers

Gbl config: 0x04_1000

Gbl timers: 0x04_1100

Table 5-4 CCSR Block Base Address Map (continued)

Block Base Address (Hex)

Block

Comments