J6: lvds connectors – IBASE IB530 User Manual

Page 20

INSTALLATIONS

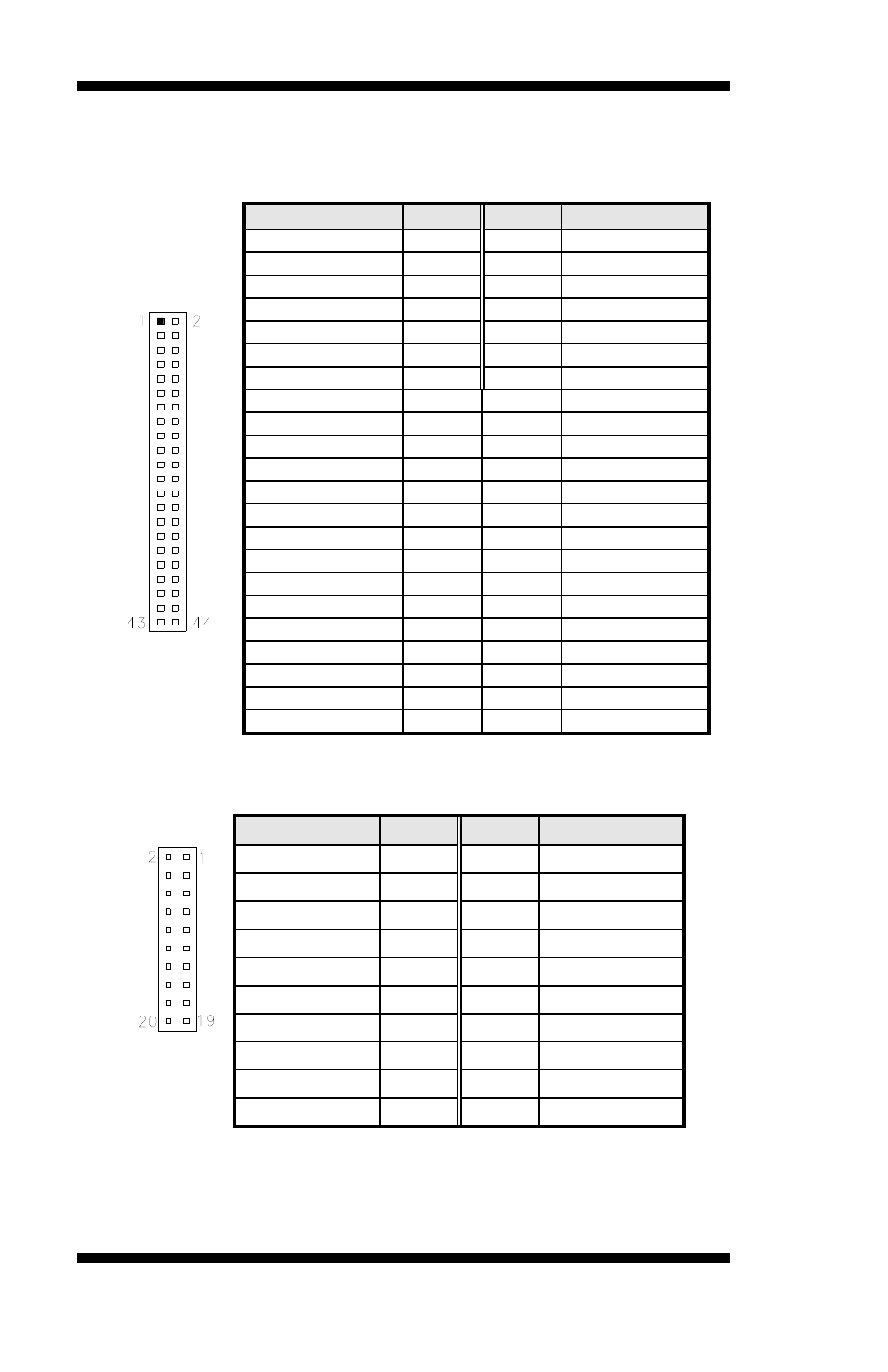

J5: TFT Panel Connector (when board supports 18-bit)

Here is the pin definition of J5 when it supports for 18-bit TFT flat panel

LCD displays.

Signal Name

Pin #

Pin #

Signal Name

+12V 1

2 +12V

Ground 3

4 Ground

5V/3.3V 5

6 5V/3.3V

N.C. 7

8

Ground

N.C. 9

10

N.C.

R0 11

12 R1

R2 13

14 R3

R4 15

16 R5

N.C. 17

18 N.C.

G0 19

20 G1

G2 21

22 G3

G4 23

24 G5

N.C. 25

26 N.C.

B0 27

28 B1

B2 29

30 B3

B4 31

32 B5

Ground 33

34 Ground

SHFCLK 35

36

FLM(VSYNC)

DISPENA(MDE)

37 38 LP(HSYNC)

Ground 39

40

ENABKL

Ground 41

42 N.C.

ENAVDD 43

44 5V/3.3V

*Depends on JP2 setting (1-2 for 3.3V / default, 2-3 for 5V).

J6: LVDS Connectors

Signal Name

Pin #

Pin #

Signal Name

TX0- 2

1 TX0+

Ground 4 3 Ground

TX1- 6

5 TX1+

5V/3.3V 8 7 Ground

TX3- 10

9 TX3+

TX2- 12

11 TX2+

Ground 14 13 Ground

TXC- 16

15 TXC+

5V/3.3V 18 17 ENABKL

+12V 20

19 +12V

*Depends on JP2 setting (1-2 for 3.3V/default, 2-3 for 5V).

16

IB530F User’s Manual