Vcntrl register – Sundance SMT128 User Manual

Page 8

Advertising

Preliminary

Page 8 of 15

SMT128 User Manual

S0INT0

->

A logic ‘1’ when and interrupt occurs on the ModBus.

S0INT1

->

A logic ‘1’ when and interrupt occurs on the RS232 Port.

These interrupt signals must be cleared via the UART Registers.

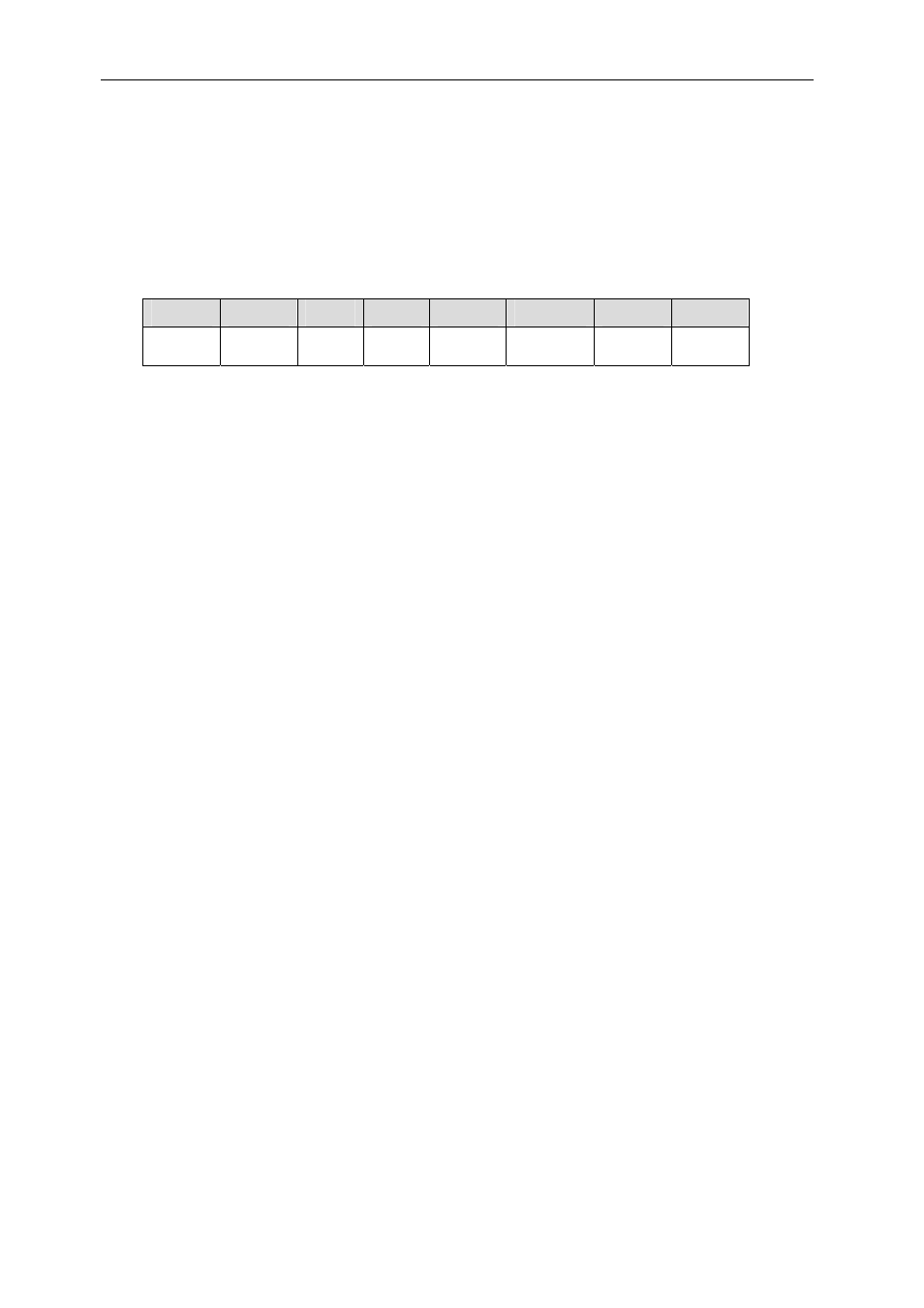

VCNTRL Register

D7

D6

D5

D4

D3

D2

D1

D0

X X X

X X

MODINTEN

RST

UART

RST

FLASH

RST UART/RST FLASH: When these bits are high the motherboard UART or FLASH

is reset.

RST UART: When logic ‘1’ the UART is in a reset state.

RST FLASH: When logic ‘0’ the FLASH is in a reset state

MODINTEN: When high MODBUS interrupt is enabled on IIOF1 of DSP.

Advertising