Sundance SMT166 User Manual

Page 18

The onboard flash used can contain up to 4 bitstreams for a 512 Mbit flash and up

to 8 for a 1Gbit flash, which is divided into equal 128Mbit regions. As standard a

512Mbit device is fitted. This is sufficient for two bitstreams for any size FPGA.

The SMT6002 software takes care about generating the correct offset/address while

writing bitstreams. The first bitstream should be stored at address 0x0 in the flash

and the second at address 0x200,0000, in order for the biggest/first bitstream to fit

without overlapping on the second bitstream.

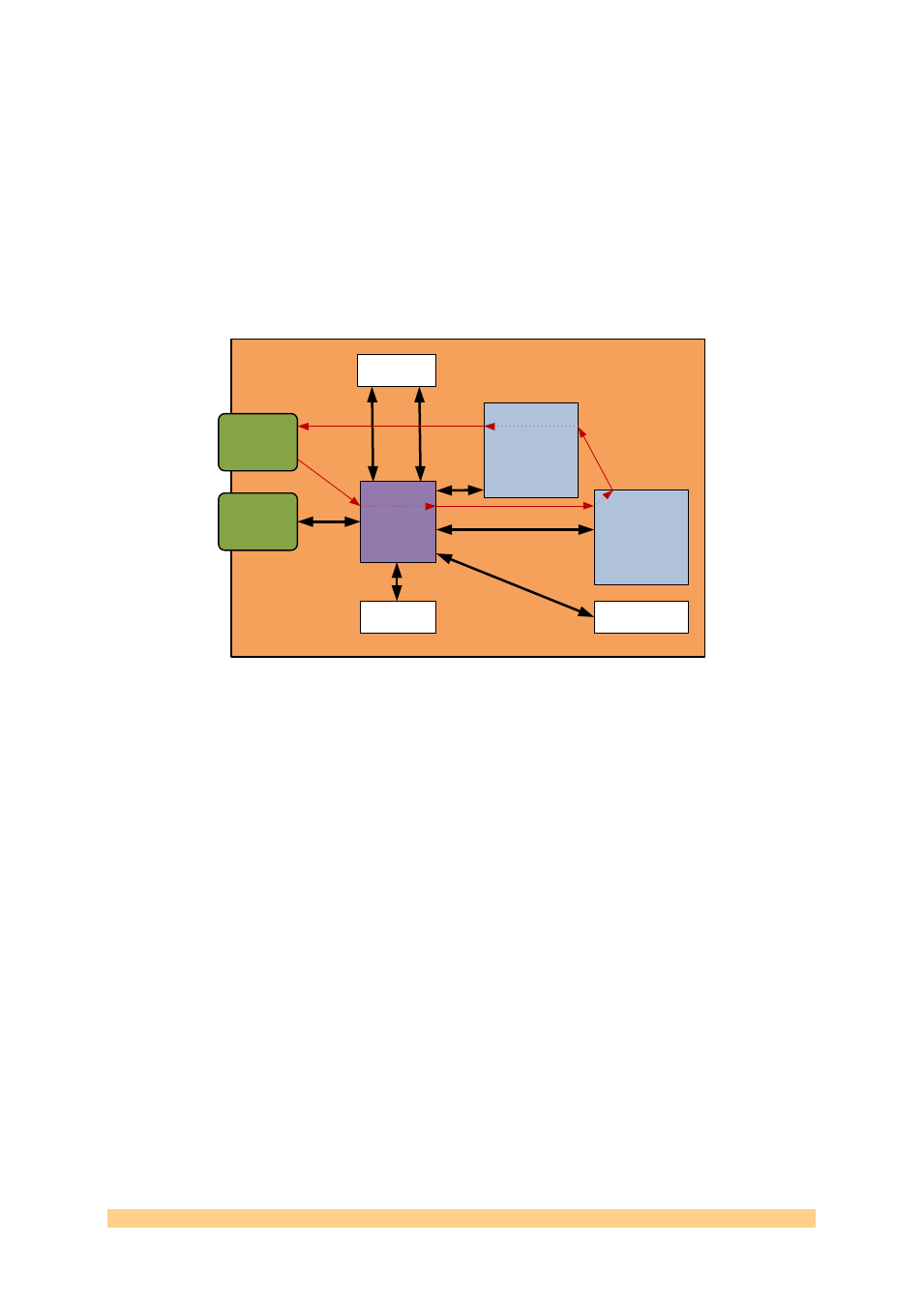

Below is a block diagram showing the connections between FPGAs, CPLD and Flash:

SMT166 – Configuration

FPGA_0

Virtex 6

LX130T-LX395T

FPGA_1

Virtex 6

LX130T-LX395T

Flash

USB2.0

CPLD

Mode selection

made via

switches

Config.

Port

Configuration Port

Comport3

Master Module

JTAG

Figure 8 - Configuration Block Diagram.

Product Specification SMT166

Page 18 of 44

Last Edited: 17/06/2014 16:12:00