Sundance SMT338 User Manual

Page 13

Version 1.5

Page 13 of 19

SMT338 User Manual

3.2. FPGA

Reconfiguration

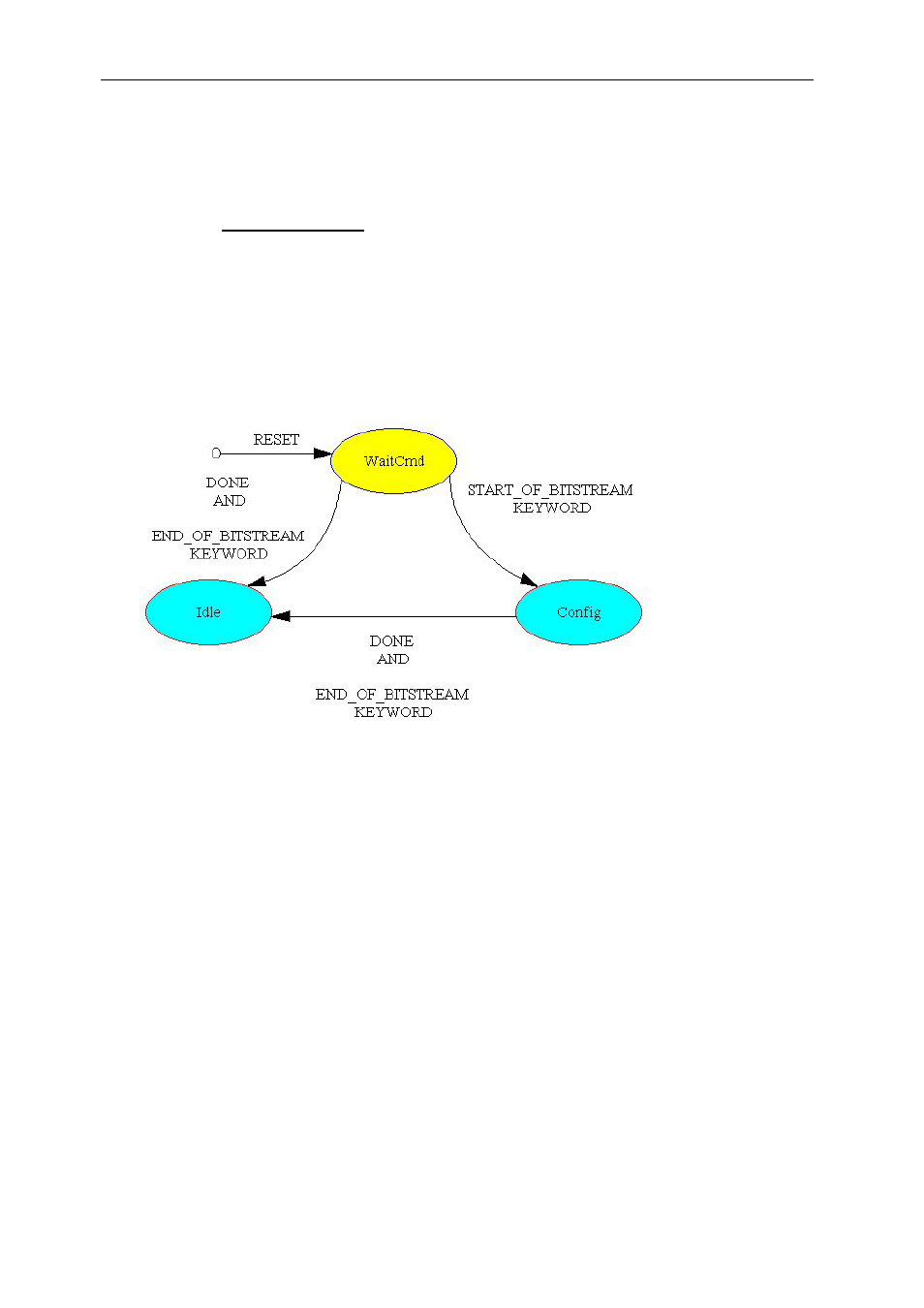

The following description is referring to Figure 8.

3.2.1. Once configured.

When a TISRESET is received by the SMT338, the CPLD and the FPGA are reset.

4) The CPLD owns Comm-Port 3 and can configure the FPGA with a new bitstream

(repeat step 2).

5) The CPLD can leave Comm-Port 3 available to the FPGA and enter an Idle state

on receiving the command BCBCBC00.

Figure 6: FPGA reconfiguration

3.3. FPGA

Reconfiguration in real time

The SMT338 can be reprogrammed on-the fly by sending a new bitstream to the

Virtex FPGA.

It is possible to reconfigure the Virtex dynamically by sending a reconfigure

command to it.

The circuit recognizing a reconfiguration request must be implemented in the FPGA,

so any user-defined command can be sent over a Comm-port for instance.

An example design is provided in the software package for the SMT338 (SMT6338).