Sundance FC202 FPGA User Manual

Page 17

Advertising

Sundance Digital Signal Processing Inc.

Rev1.0

4790 Caughlin Parkway 233, Reno, NV 89519-0907, U.S.A.

Tel: +1 (775) 827-3103, Fax: +1 (775) 827-3664, email:

www.sundance.com

..\fc202_ea1\simulink\fc202_fpga\

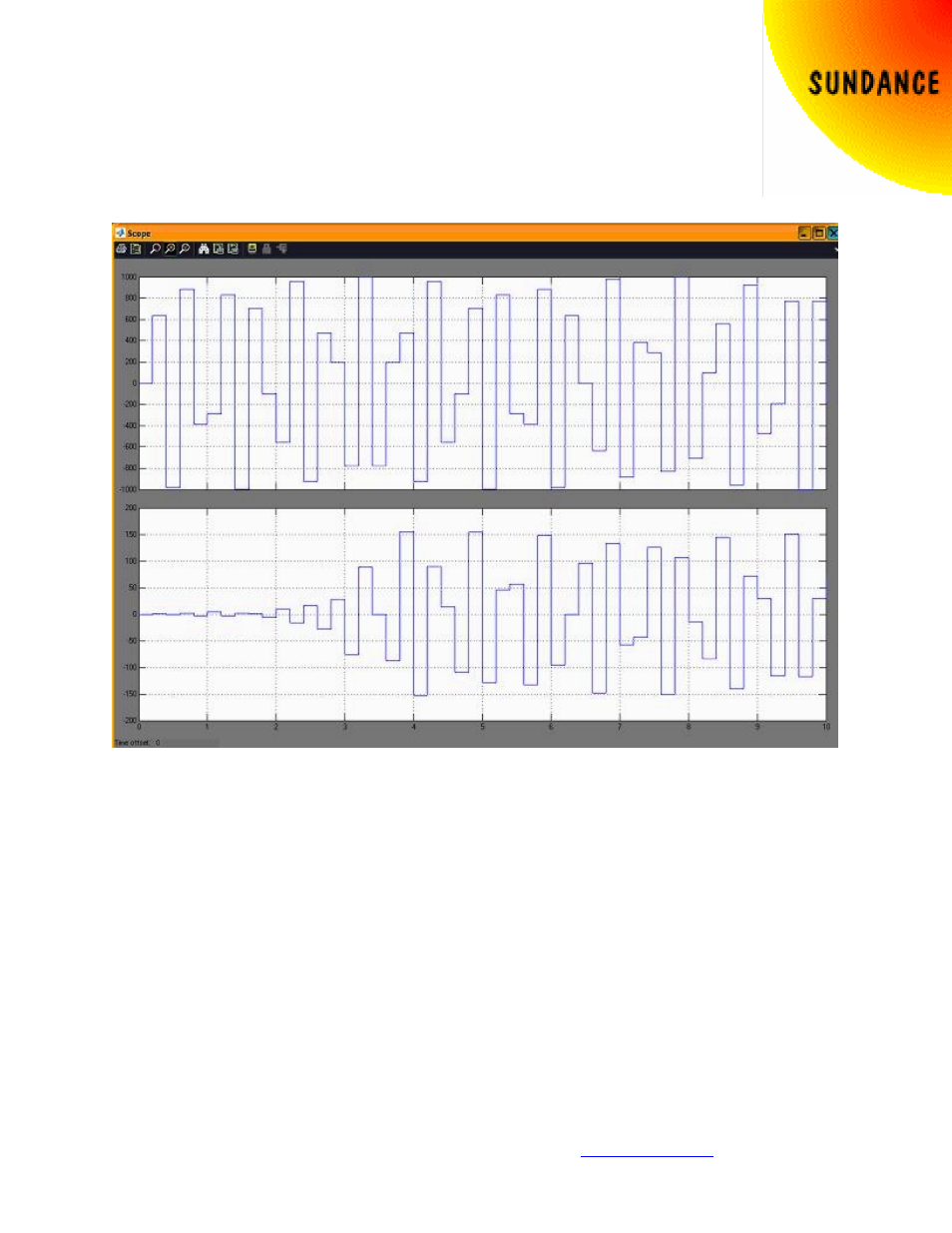

Figure 5 - In-Phase and Quadrature output generated by DSP model

The PARS generated test bench “Subsystem2_TestBench.mdl” can be found under

..\fc202_ea1\simulink\fc202_dsp\fc202_dsp_PARS\

Figure 6 below shows the results generated by the actual core executed on an FPGA.

The delay in the In-Phase signal is due to the hardware delay. This cannot be seen in the DSP

model above as the Hilbert transform component is implemented only for the Quadrature

output.

Advertising