Altpll ip core references, Altpll parameters, Operation modes parameter settings – Altera MAX 10 Clocking and PLL User Manual

Page 67: Altpll ip core references -1, Altpll parameters -1, Operation modes parameter settings -1

ALTPLL IP Core References

6

2014.12.15

UG-M10CLKPLL

ALTPLL Parameters

The following tables list the IP core parameters applicable to MAX 10 devices.

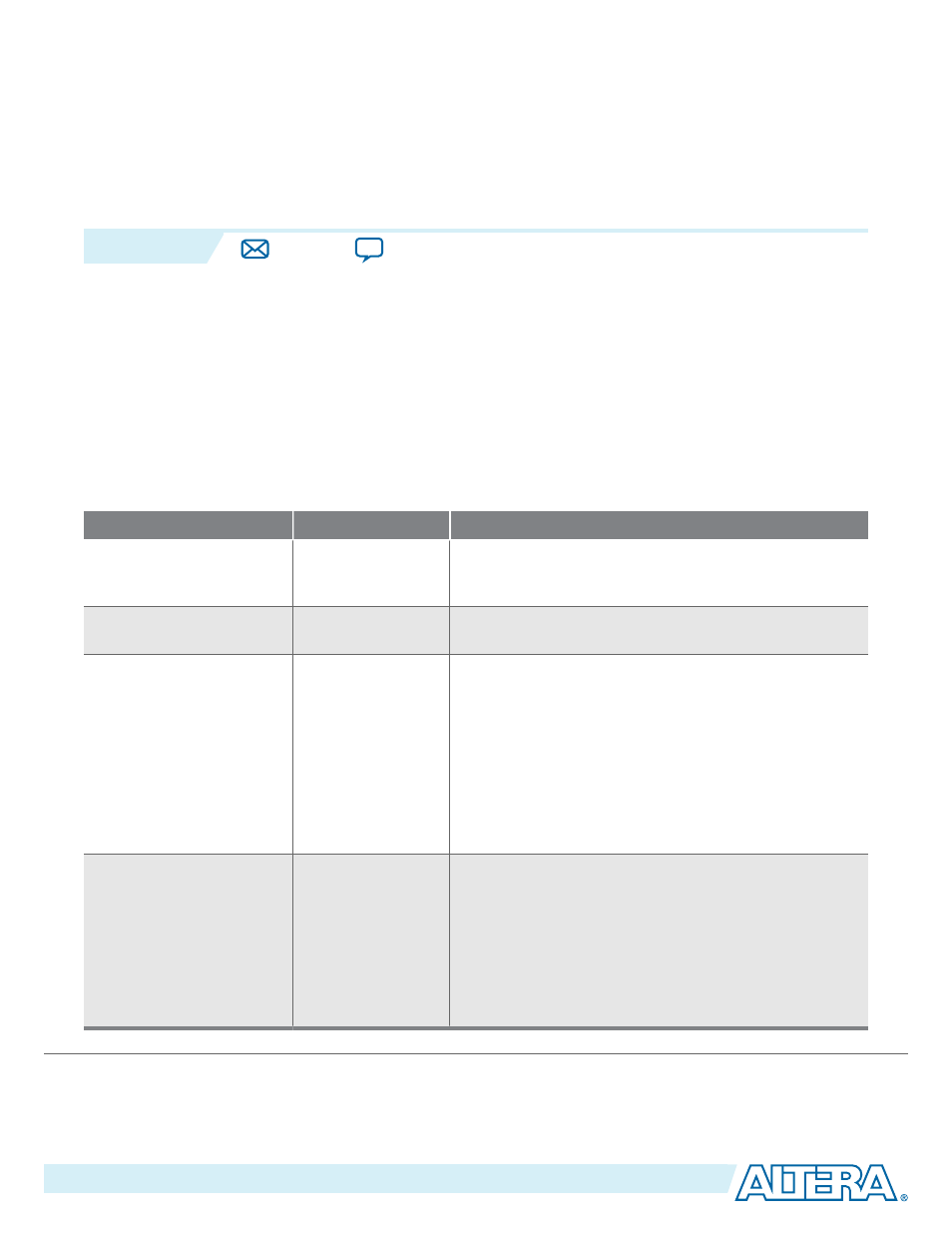

Operation Modes Parameter Settings

You can set the operation mode for PLL in the General/Modes page of the ALTPLL IP core parameter

editor.

Table 6-1: Operation Mode Parameter Editor Settings

Parameter

Value

Description

Which device speed

grade will you be using?

Any, 7, or 8

Specify the speed grade if you are not already using a

device with the fastest speed. The lower the number, the

faster the speed grade.

What is the frequency of

the inclock0 input?

—

Specify the frequency of the input clock signal.

Use the feedback path

inside the PLL

In normal mode, In

source-synchronous

compensation

mode, In zero-delay

buffer mode, or

With no

compensation

Specify which operation mode to use.

For source-synchronous mode and zero-delay buffer

mode, you must make PLL Compensation assignments

using the Assignment Editor in addition to setting the

appropriate mode in the IP core. The assignment allows

you to specify an output pin as a compensation target

for a PLL in zero-delay buffer mode, or to specify an

input pin or group of input pins as compensation

targets for a PLL in source-synchronous mode.

Which output clock will

be compensated for?

C0

,

C1

,

C2

,

C3

, or

C4

Specify which PLL output port to compensate.

The drop down list contains all output clock ports for

the selected device. The correct output clock selection

depends on the operation mode that you select.

For example, for normal mode, select the core output

clock. For zero-delay buffer mode, select the external

output clock.

©

2015 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, ENPIRION, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are

trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as

trademarks or service marks are the property of their respective holders as described at

www.altera.com/common/legal.html

. Altera warrants performance

of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any

products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information,

product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device

specifications before relying on any published information and before placing orders for products or services.

www.altera.com

101 Innovation Drive, San Jose, CA 95134