Encoding latency –5, Encoding latency – Altera 8B10B Encoder/Decoder MegaCore Function User Manual

Page 23

Chapter 3: Specifications

3–5

Functional Description

May 2011

Altera Corporation

8B10B Encoder/Decoder MegaCore Function User Guide

If the encoded words are to be transmitted serially, the result of encoding

datain[15:8]

should be transmitted first.

Encoding Latency

When the register inputs/outputs parameter is turned on, the encoder is pipelined,

thus it takes three clock cycles for a character to be encoded. The encoded value—

corresponding to the values of

datain

and

kin

sampled by the encoder on rising edge

n

—is output shortly after rising edge

n+2

, and is available to be sampled on the rising

edge of clock cycle

n+3

. (See

Figure 3–5 on page 3–6

). To enable cascaded encoding,

the data paths fed by the

rdforce

and

rdin

inputs are not pipelined. Because

rdforce

and

rdin

are normally only used in cascaded configurations, this should not be a

problem. In cases where the

rdforce

and

rdin

inputs are to be used in noncascaded

configurations, they should be delayed two clock cycles with respect to their

corresponding

datain

and

kin

values.

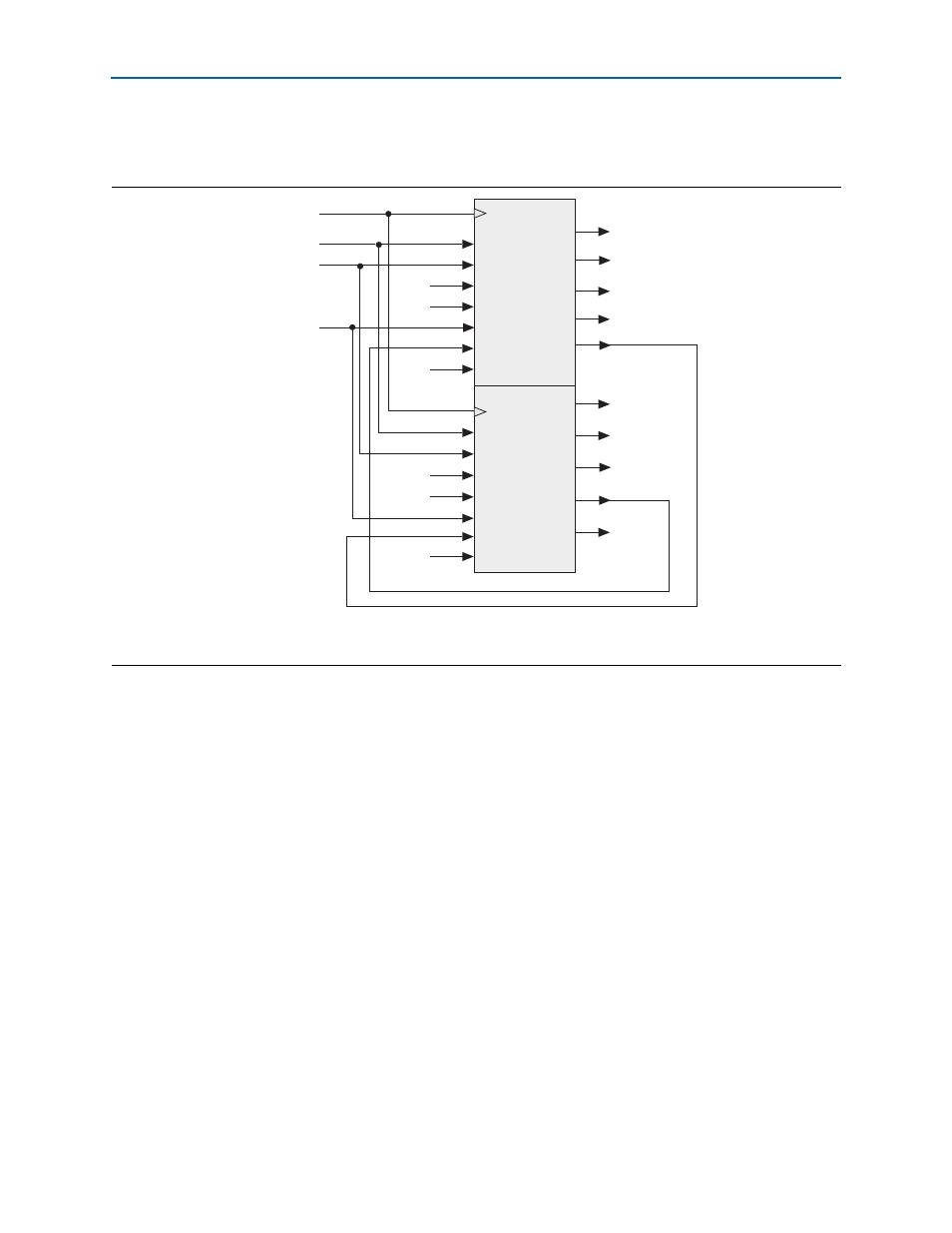

Figure 3–4. Cascaded Encoding

Note to

Figure 3–4

:

(1) The

ena

,

idle_ins

, and

rdforce

signals are set high (logic 1).

clk

reset_n

rdout

valid

kerr

clk

reset_n

rdcascade

valid

kerr

rdout

rdin

dataout [19:10]

rdcascade

rdin

[1:0]

kin

[15:0]

datain

ena

rdforce

ena

rdforce

datain [7:0]

datain [15:8]

dataout [9:0]

kin [0]

kin [1]

idle_ins

idle_ins