Altera Cyclone V GX FPGA User Manual

Page 13

Chapter 4: Development Board Setup

4–3

Factory Default Switch Settings

October 2012

Altera Corporation

Cyclone V GX FPGA Development Kit

User Guide

2. Set the DIP switch bank (SW4) to match

and

.

3. Set the DIP switch bank (SW5) to match

and

.

3

FACT LOAD

Switch 3 has the following options:

■

On (0) = Load the user design from flash at

power up.

■

Off (1) = Load the user factory from flash at

power up.

Off

4

SEC MODE

Switch 4 has the following options:

■

On (0) = On-Board USB Blaster II sends

FACTORY command at power up

■

Off (1) = On-Board USB Blaster II does not

send FACTORY command at power up

Off

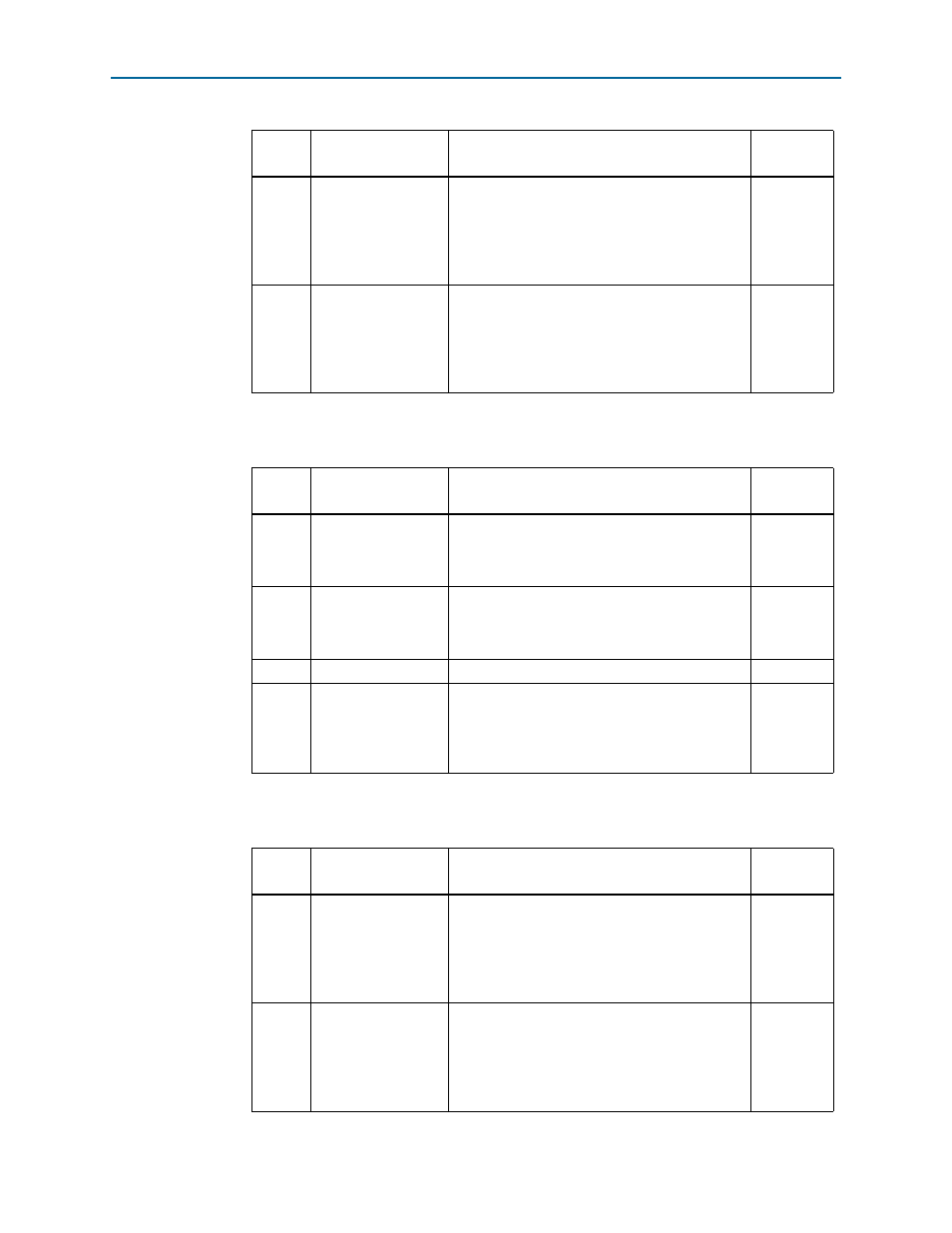

Table 4–2. SW4 DIP Switch Settings

Switch

Board

Label

Function

Default

Position

1

PCIE_PRSNT2n_x1

Switch 1 has the following options:

■

On (0) = x1 presence detect is enabled.

■

Off (1) = x1 presence detect is disabled.

Off

2

PCIE_PRSNT2n_x4

Switch 2 has the following options:

■

On (0) = x4 presence detect is enabled.

■

Off (1) = x4 presence detect is disabled.

Off

3

—

—

—

4

FAN_FORCE_ON

Switch 4 has the following options: (Fan is not

included.)

■

On (0) = Fan is turned on.

■

Off (1) = Fan is turned off

Off

Table 4–3. SW5 JTAG DIP Switch Settings (Part 1 of 2)

Switch

Board

Label

Function

Default

Position

1

5M2210_JTAG_EN

Switch 1 has the following options:

■

On (0) = Do not Include MAX V system

controller in the JTAG chain.

■

Off (1) = Include MAX V system controller in

the JTAG chain

Off

2

HSMA_JTAG_EN

Switch 2 has the following options:

■

On (0) = Do not Include the HSMC Port A in the

JTAG chain.

■

Off (1) = Include the HSMC Port A in the JTAG

chain.

On

Table 4–1. SW3 DIP Switch Settings (Part 2 of 2)

Switch

Board

Label

Function

Default

Position