Altera Viterbi Compiler User Manual

Page 33

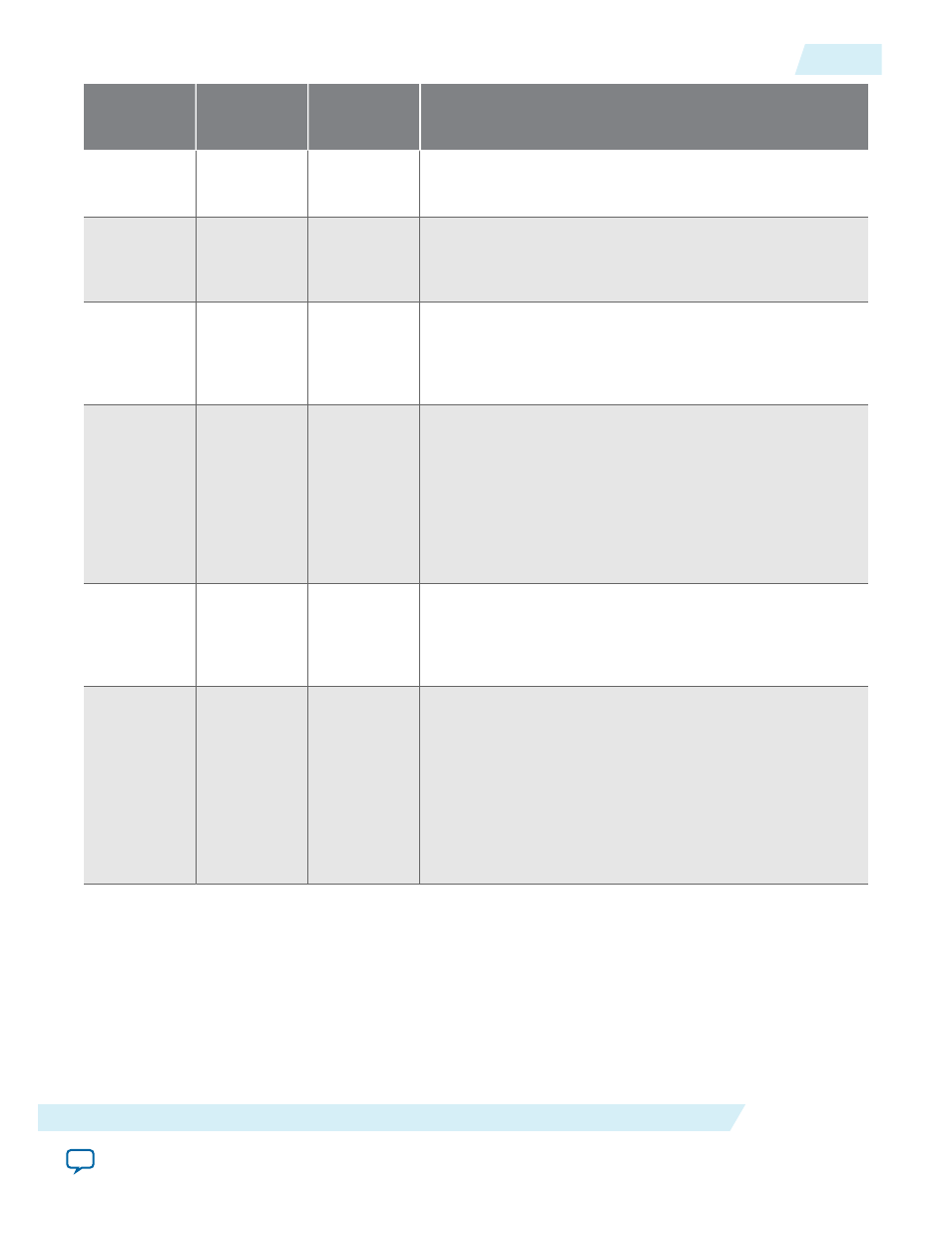

Signal Name

Avalon-ST

Name

Direction

Description

eras_

sym[Nmax

:1]

dat

Input

When asserted,

eras_sym

Indicates an erased symbol. Both

rr

and

eras_sym

are Avalon-ST

dat

inputs

rr

dat

Input

Data input, which takes in n symbols, each softbits wide per

clock. In TCM mode the

rr

width is (2N × softbits:1); in

Viterbi mode the

rr

width is (nmax × softbits:1).Both

rr

and

eras_sym

are Avalon-ST

dat

inputs

sink_eop

eop

Input

End of packet (block) signal.

sink_eop

delineates the packet

boundaries on the

rr

bus. When

sink_eop

is high, the end

of the packet is present on the

dat

bus.

sink_eop

is asserted

on the last transfer of every packet. This signal applies to

block decoding only.

sink_rdy

ready

Output

Data transfer enable signal.The interface sink drives

sink_

rdy

and controls the flow of data across the interface.

sink_

rdy

behaves as a read enable from sink to source. When the

source observes

sink_rdy

asserted on the

clk

rising edge, it

can drive the Avalon-ST data interface signals and assert

sink_val

as early as the next clock cycle, if data is available.

In the hybrid architecture,

sink_rdy

is asserted for one

clock cycle at a time. If data is not available at the time, you

have to wait for the next

sink_rdy

pulse.

sink_sop

sop

Input

Start of packet (block) signal.

sop

delineates the packet

boundaries on the

rr

bus. When

sink_sop

is high, the start

of the packet is present on the

rr

bus.

sink_sop

is asserted

on the first transfer of every packet This signal applies to

block decoding only.

sink_val

val

Input

Data valid signal.

sink_val

indicates the validity of the data

signals.

sink_val

is updated on every clock edge where

sink_rdy

is sampled asserted, and holds its current value

along with the

dat

bus where

sink_rdy

is sampled

deasserted. When

sink_val

is asserted, the Avalon-ST data

interface signals are valid. When

sink_va

l is deasserted, the

Avalon-ST data interface signals are invalid and you must

disregard them. To determine whether new data has been

received, the sink qualifies the

sink_val

signal with the

previous state of the

sink_rdy

signal.

UG-VITERBI

2014.12.15

Avalon-ST Sink Signals

3-15

Viterbi IP Core Functional Description

Altera Corporation