Status signals, Viterbi ip core timing diagrams, Status signals -18 – Altera Viterbi Compiler User Manual

Page 36: Viterbi ip core timing diagrams -18

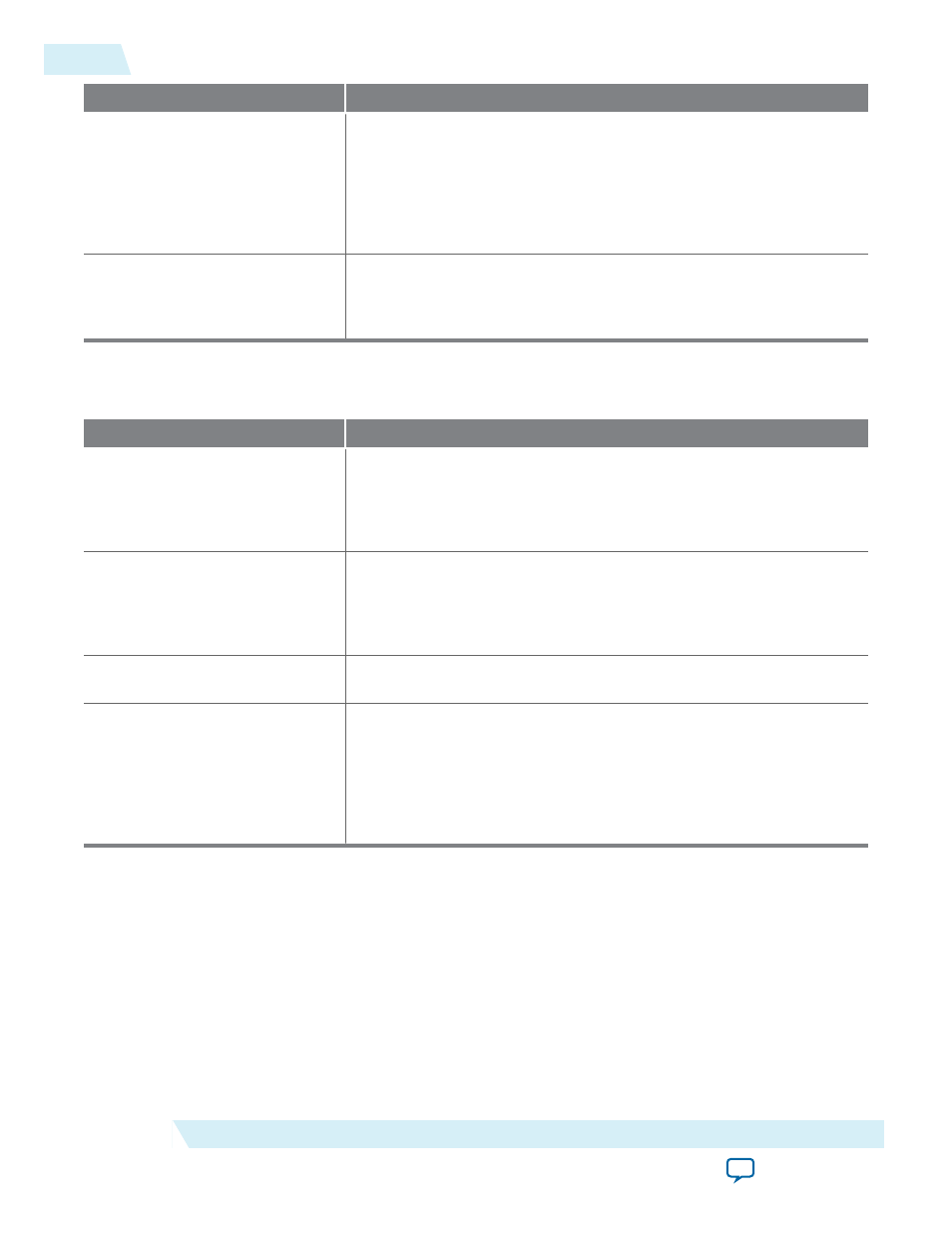

Signal Name

Description

tb_type

Altera recommends that you set

tb_type

high always for future

compatibility. In block decoding when

tb_type

is low, the decoder

starts from state 0; when

tb_type

is high, the decoder uses the state

specified in

tr_init_state[(L-1):1]

. For block decoding set

tb_

type

high. The IP core latches

tb_type

when

sink_eop

is asserted. If

you select None or Continuous optimization, the IP core connects this

input to zero.

tr_init_state[(L-1):1]

Specifies the state to start the traceback from, when

tb_type

is asserted

high. The IP core latches

tr_init_state

when

sink_eop

is asserted. If

you select continuous optimization, this input is removed from the top

level design and connected to zero in the inner core.

Status Signals

Signal

Description

bestadd[(L-1):1]

The best address state. The address corresponding to the best metric as

it is being found by the best state finder. The metric of this state if

shown in

bestmet

. If you select Continuous or None optimization and

turn off best state finder, the IP core leaves this signal open. For parallel

decoders, the IP core removes this signal.

bestmet[bmgwide:1]

The best metric. The

bestmet

signal shows the best state metric for

every trellis step as the best state finder finds it. The state that contains

this best metric is shown in

bestadd

. If you select Continuous or

None for optimization and turn off best state finder, the IP core leave

this signal open, For parallel decoders, the IP core removes this signal.

normalizations[8:1]

The normalizations bus indicates in real time the number of normali‐

zations that occur since you activated

sink_sop

.

numerr[]

The

numerr

bus contains the number of errors detected during a block.

The iP core updates it each time it detects an error, so you can see the

location of individual errors. It is reset when

source_sop

asserted; it is

valid two-clock cycles after

source_sop

. The wizard automatically sets

the width of this bus. If you do not select a BER block, the IP cores

leaves this signal open. Only available when you select the BER

estimator option

Viterbi IP Core Timing Diagrams

3-18

Status Signals

UG-VITERBI

2014.12.15

Altera Corporation

Viterbi IP Core Functional Description