Configuration signals, Configuration signals -17 – Altera Viterbi Compiler User Manual

Page 35

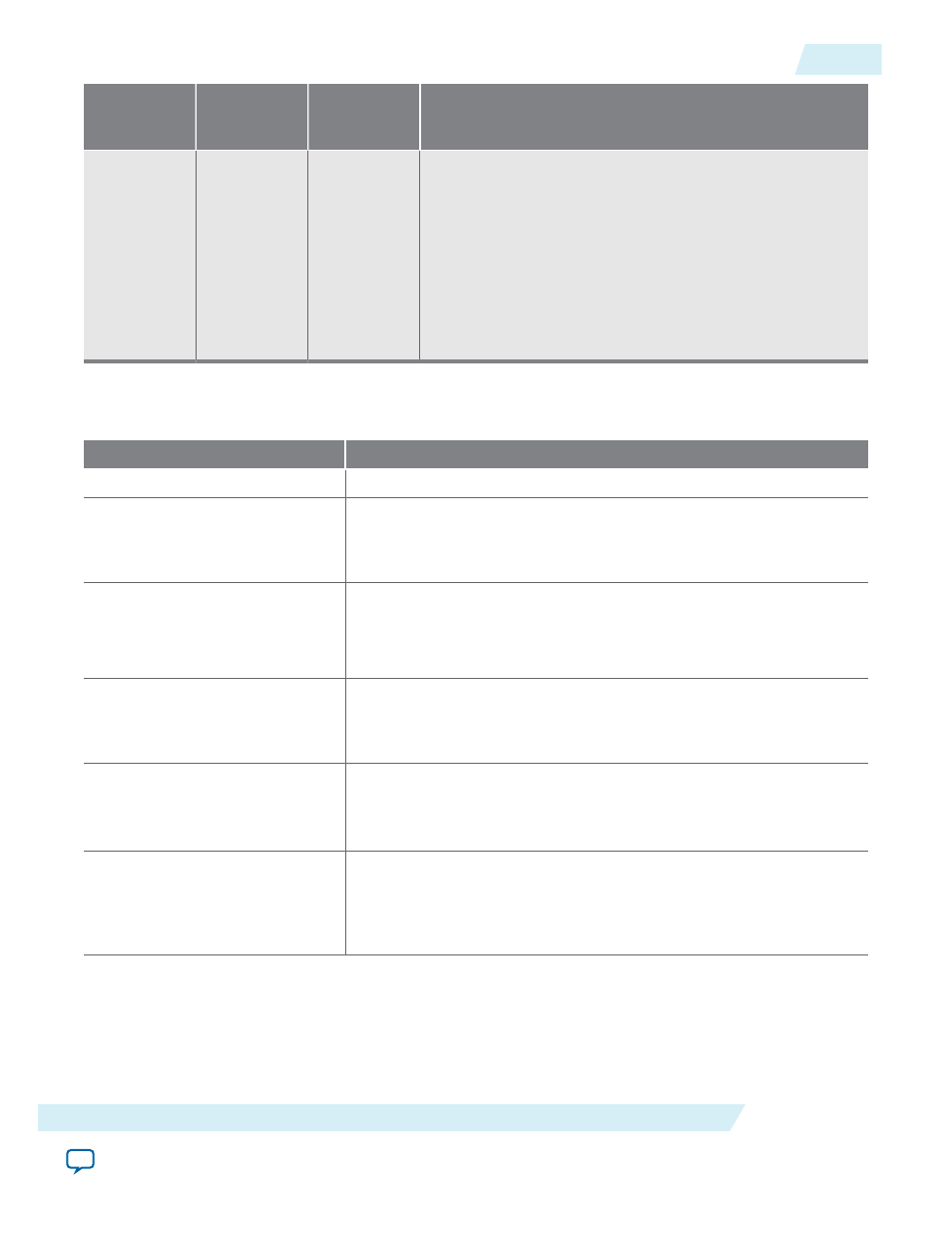

Signal

Avalon-ST

Name

Direction

Description

out_data

data

Output

In Qsys systems, this Avalon-ST-compliant data bus

includes all the Avalon-ST output data and configuration

signals. The signals are in the following order from MSB to

LSB:

•

Numerr

•

BestAdd

•

BestMet

•

Normalizations

•

Decbit

Configuration Signals

Signal Name

Description

ber_clear

Reset for the BER counter. Only for the BER block option.

bm_init_state[(L-1):1]

Specifies the state in which to initialize with the value from the

bm_

init_value[]

bus. All other state metrics are set to zero. the IP core

latches

bm_init_state

when

sink_sop

is asserted. Hybrid architec‐

ture only

bm_init_value[(L-1):1]

Specifies the value of the metric that initializes the start state. All other

metrics are set to 0.

bm_init_value

must be larger than (L × 2

(softbits –

1)

). the IP core latches

bm_init_value

when

sink_sop

is asserted.

Hybrid architecture only

sel_code[log2(Ncodes):1]

Selects the codeword. ’0’ selects the first codeword, ‘1’ selects the

second, and so on. The bus size increases according to the number of

codes specified. The IP core latches

sel_code

when

sink_sop

is

asserted.

state_node_sync[log2(Nmax):1] Specifies the node synchronization rotation to

rr

.

The IP core latches

state_node_sync

signal when

sink_sop

is

asserted. Available only when you turn on Node Sync.

tb_length[]

Traceback length. The maximum width of

tb_length

is equal to the

maximum value of parameter v. The IP core latches

tb_length

input

when

sink_sop

is asserted. This IP core disables this signal if you select

the continuous optimization: you must then remove it from the

testbench.

UG-VITERBI

2014.12.15

Configuration Signals

3-17

Viterbi IP Core Functional Description

Altera Corporation