Altera Viterbi Compiler User Manual

Page 7

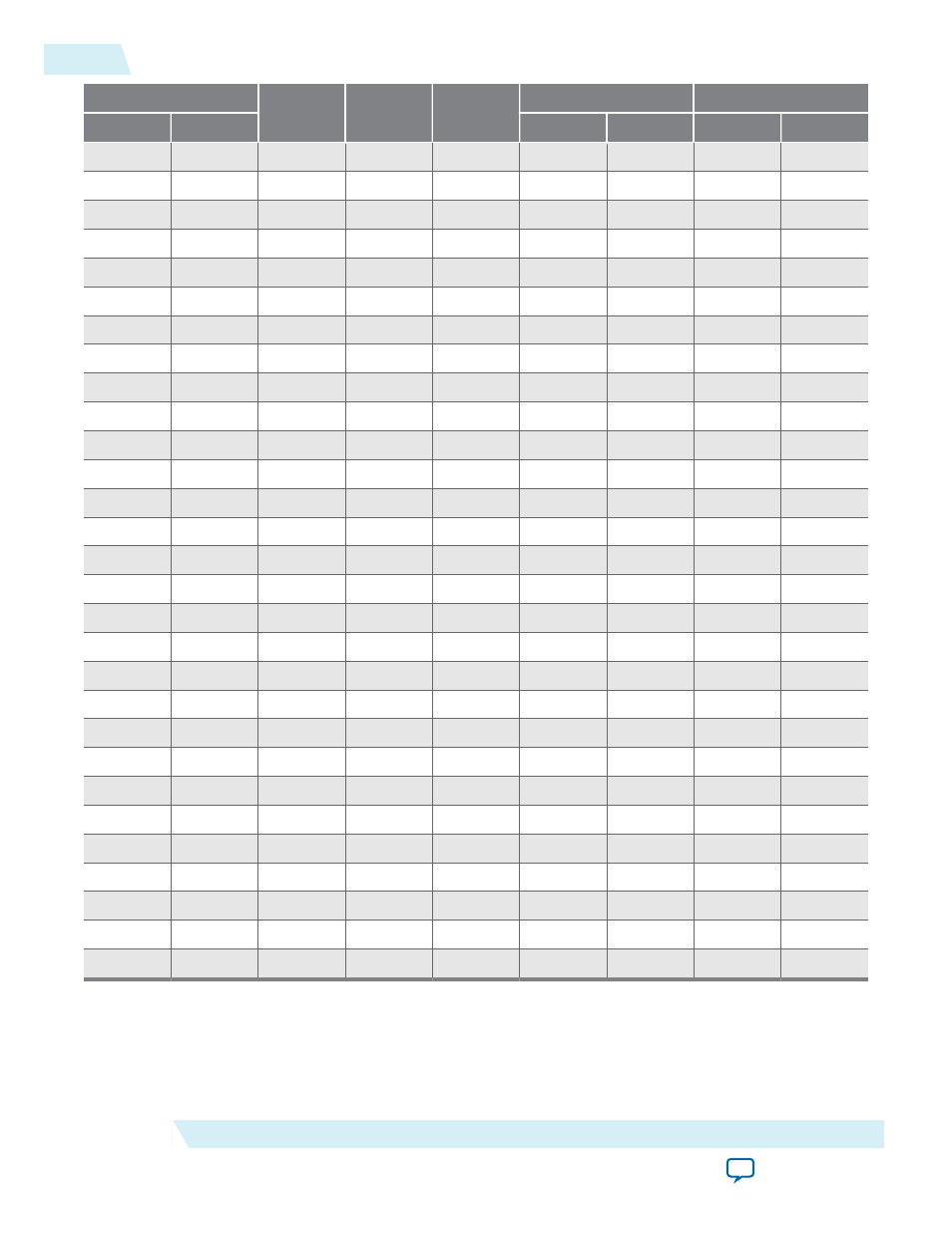

Parameters

Device

ALM

f

MAX

(MHz)

Memory

Registers

L

A

M10K

M20K

Primary

Secondary

7

1

Arria V

427

207

6

--

507

58

7

1

Cyclone V 427

185

6

--

507

74

7

1

Stratix V

417

438

--

6

506

51

7

2

Arria 10

622

363

--

4

670

51

7

2

Arria V

529

215

6

--

625

71

7

2

Cyclone V 532

180

6

--

625

74

7

2

Stratix V

502

408

--

6

625

56

7

4

Arria 10

835

366

--

4

885

101

7

4

Arria V

744

204

6

--

856

99

7

4

Cyclone V 746

173

6

--

856

100

7

4

Stratix V

652

382

--

6

856

82

9

1

Arria 10

932

343

--

9

970

88

1

Arria V

792

190

11

--

927

90

9

1

Cyclone V 794

176

11

--

926

96

9

1

Stratix V

777

393

--

11

924

94

9

16

Arria V

2,118

188

17

--

2,743

309

9

16

Cyclone V 2,119

163

17

--

2,744

275

9

16

Stratix V

1,887

348

--

17

2,738

198

9

2

Arria 10

1,029

363

--

9

1,091

74

9

2

Arria V

889

205

11

--

1,053

98

9

2

Cyclone V 889

180

11

--

1,053

96

9

2

Stratix V

883

377

--

11

1,053

115

9

4

Arria 10

1,240

298

--

9

1,321

87

9

4

Arria V

1,097

201

11

--

1,302

137

9

4

Cyclone V 1,096

159

11

--

1,302

126

9

4

Stratix V

1,021

390

--

11

1,302

119

9

8

Arria V

1,465

197

13

--

1,788

193

9

8

Cyclone V 1,465

163

13

--

1,789

191

9

8

Stratix V

1,398

351

--

13

1,790

154

1-4

Viterbi IP Core Performance and Resource Utilization

UG-VITERBI

2014.12.15

Altera Corporation

About the Viterbi IP Core